RL78/G1H CHAPTER 13 A/D CONVERTER

R01UH0575EJ0120 Rev. 1.20 Page 290 of 920

Dec 22, 2016

Note These are the numbers of clock cycles when conversion is with 10-bit resolution. When eight-bit resolution is selected,

the values are shorter by two cycles of the conversion clock (f

AD).

Caution 1. The A/D conversion time must also be within the relevant range of conversion times (tCONV) described in 31.6.1

A/D converter characteristics

Caution 2. Rewrite the FR2 to FR0, LV1 and LV0 bits to other than the same data while conversion is stopped (ADCS = 0,

ADCE = 0).

Caution 3. The above conversion time does not include conversion state time. Conversion state time add in the first

conversion. Select conversion time, taking clock frequency errors into consideration.

Remark

fCLK: CPU/peripheral hardware clock frequency

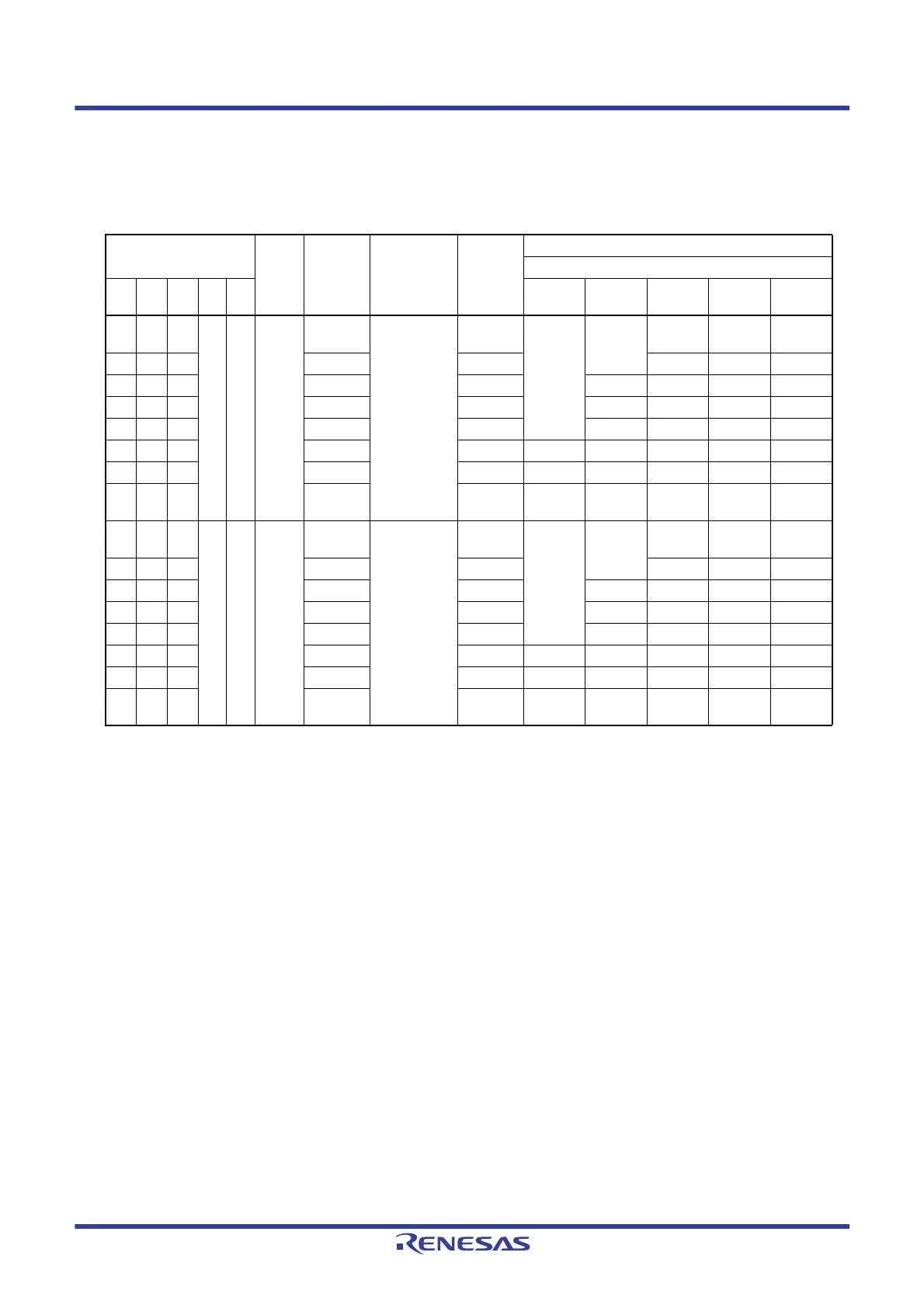

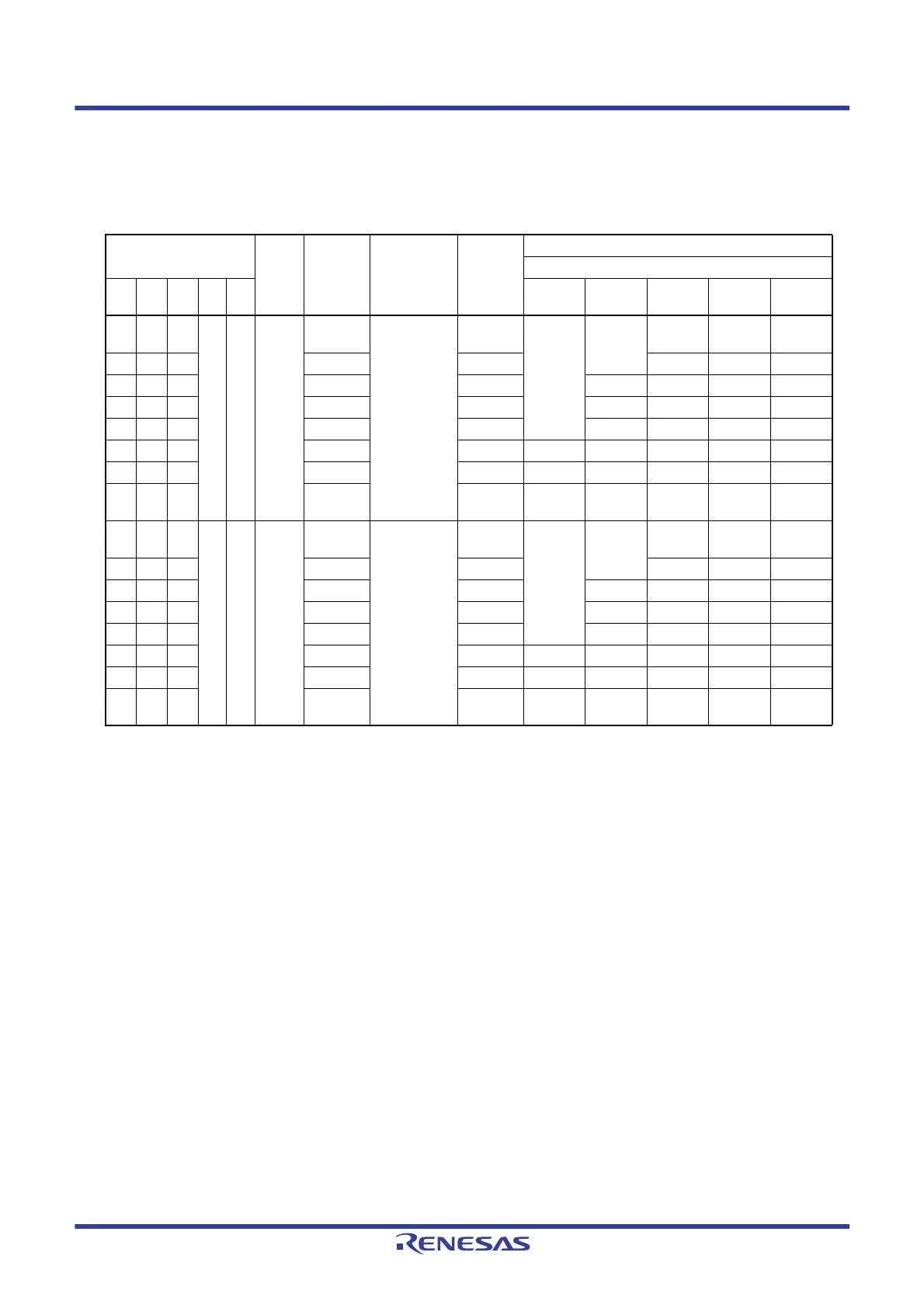

Table 13 - 3 A/D Conversion Time Selection (1/4)

(1) When there is no A/D power supply stabilization wait time Normal mode 1, 2

(software trigger mode/hardware trigger no-wait mode)

A/D Converter Mode

Register 0 (ADM0)

Mode Conversion

Clock (f

AD)

Number of

Conversion

Clock

Note

Conversion

Time

Conversion Time at 10-Bit Resolution

2.7 V

≤ VDD ≤ 3.6 V

FR2 FR1 FR0 LV1 LV0 f

CLK =

1 MHz

fCLK =

4 MHz

fCLK =

8 MHz

fCLK =

16 MHz

fCLK =

32 MHz

0 0 0 0 0 Normal

1

f

CLK/64 19 fAD

(number of

sampling clock:

7 f

AD)

1216/f

CLK Setting

prohibited

Setting

prohibited

Setting

prohibited

76 μs38 μs

001 f

CLK/32 608/fCLK 76 μs 38 μs19 μs

010 f

CLK/16 304/fCLK 76 μs 38 μs 19 μs9.5 μs

011 f

CLK/8 152/fCLK 38 μs 19 μs9.5 μs 4.75 μs

100 f

CLK/6 114/fCLK 28.5 μs 14.25 μs 7.125 μs 3.5625 μs

101 f

CLK/5 95/fCLK 95 μs23.75 μs 11.875 μs 5.938 μs 2.9688 μs

110 f

CLK/4 76/fCLK 76 μs19 μs9.5 μs 4.75 μs 2.375 μs

111 f

CLK/2 38/fCLK 38 μs9.5 μs4.75 μs 2.375 μs Setting

prohibited

0 0 0 0 1 Normal

2

f

CLK/64 17 fAD

(number of

sampling clock:

5 f

AD)

1088/f

CLK Setting

prohibited

Setting

prohibited

Setting

prohibited

68 μs34 μs

001 f

CLK/32 544/fCLK 68 μs 34 μs17 μs

010 f

CLK/16 272/fCLK 68 μs 34 μs 17 μs8.5 μs

011 f

CLK/8 136/fCLK 34 μs 17 μs8.5 μs 4.25 μs

100 f

CLK/6 102/fCLK 25.5 μs 12.75 μs 6.375 μs 3.1875 μs

101 f

CLK/5 85/fCLK 85 μs21.25 μs 10.625 μs 5.3125 μs 2.6563 μs

110 f

CLK/4 68/fCLK 68 μs17 μs8.5 μs 4.25 μs 2.125 μs

111 f

CLK/2 34/fCLK 34 μs8.5 μs4.25 μs 2.125 μs Setting

prohibited

Loading...

Loading...