RL78/G1H CHAPTER 15 SERIAL INTERFACE IICA

R01UH0575EJ0120 Rev. 1.20 Page 435 of 920

Dec 22, 2016

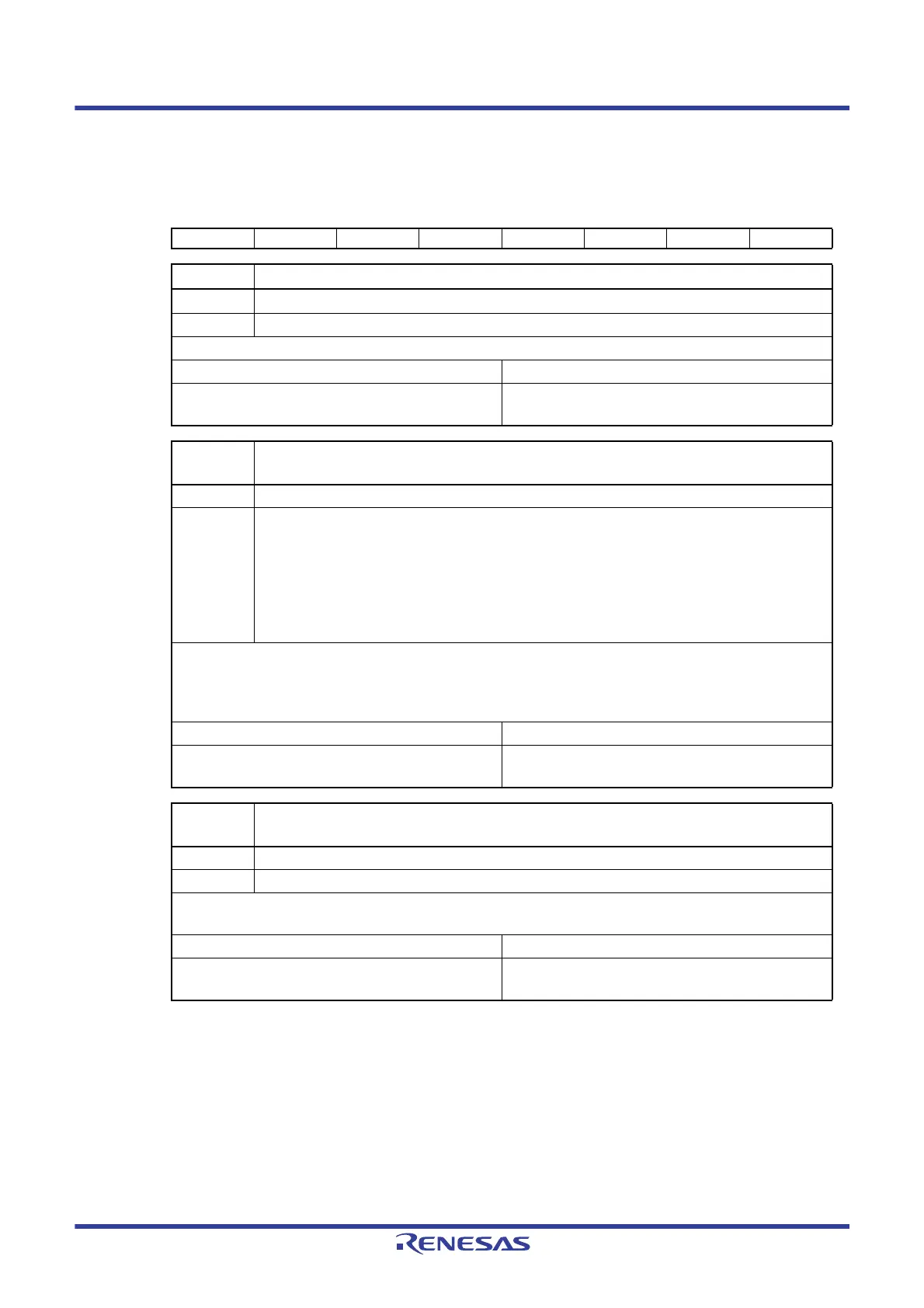

Figure 15 - 6 Format of IICA control register n0 (IICCTLn0) (1/4)

Note 1. The IICA shift register n (IICAn), the STCFn and IICBSYn bits of the IICA flag register n (IICFn), and the

CLDn and DADn bits of IICA control register n1 (IICCTLn1) are reset.

Note 2. The signal of this bit is invalid while IICEn is 0.

Note 3. When the LRELn and WRELn bits are read, 0 is always read.

Caution If the operation of I

2

C is enabled (IICEn = 1) when the SCLAn line is high level, the SDAAn line is low

level, and the digital filter is turned on (DFCn bit of IICCTLn1 register = 1), a start condition will be

inadvertently detected immediately. In this case, set (1) the LRELn bit by using a 1-bit memory

manipulation instruction immediately after enabling operation of I

2

C (IICEn = 1).

Remark

n = 0, 1

Address: F0230H (IICCTL00), F0238H (IICCTL10) After reset: 00H R/W

Symbol <7> <6> <5> <4> <3> <2> <1> <0>

IICCTLn0 IICEn LRELn WRELn SPIEn WTIMn ACKEn STTn SPTn

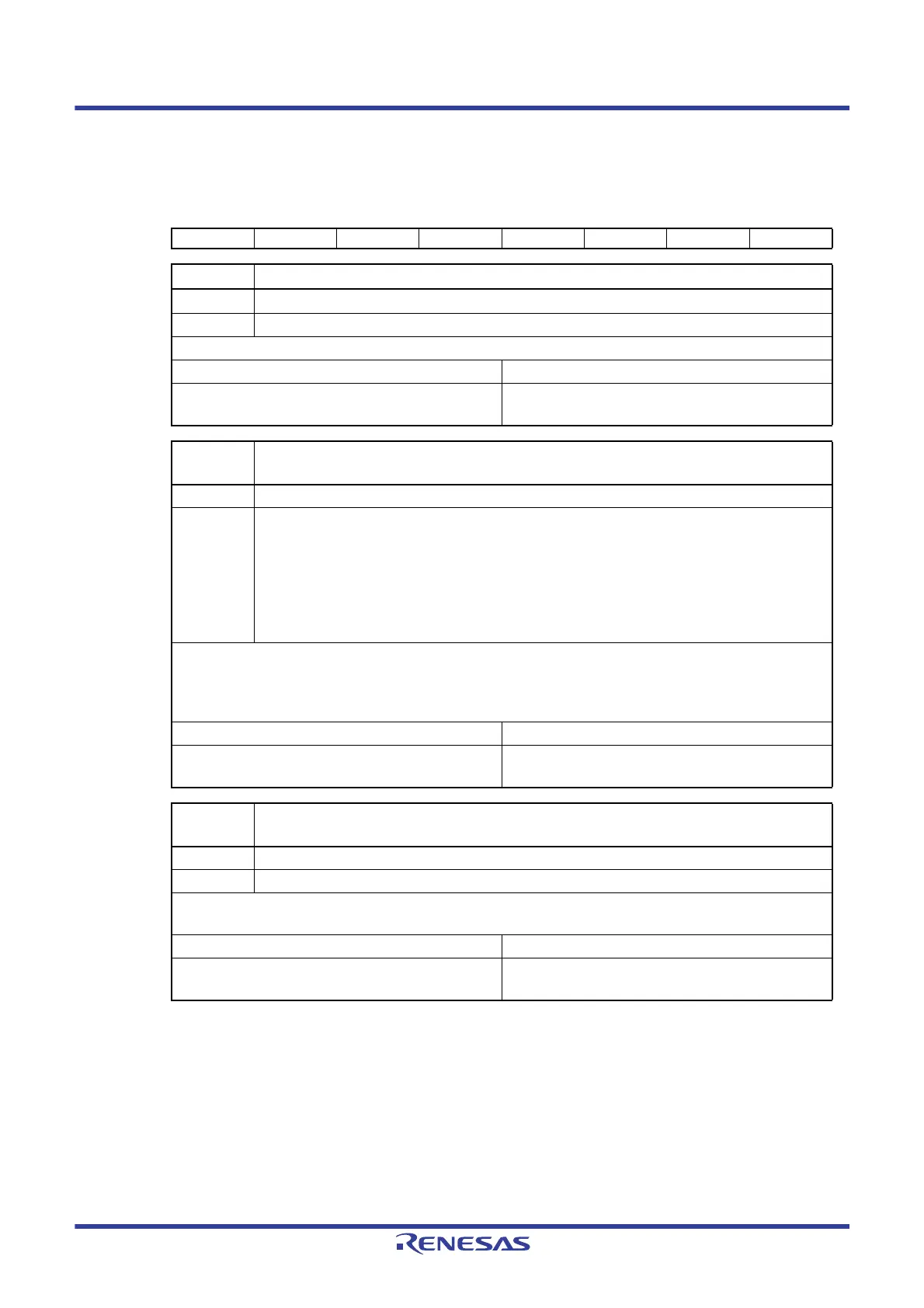

IICEn

I

2

C operation enable

0

Stop operation. Reset the IICA status register n (IICSn)

Note 1

. Stop internal operation.

1 Enable operation.

Be sure to set this bit (1) while the SCLAn and SDAAn lines are at high level.

Condition for clearing (IICEn = 0) Condition for setting (IICEn = 1)

• Cleared by instruction

• Reset

• Set by instruction

LRELn

Notes 2, 3

Exit from communications

0 Normal operation

1 This exits from the current communications and sets standby mode. This setting is automatically cleared

to 0 after being executed.

Its uses include cases in which a locally irrelevant extension code has been received.

The SCLAn and SDAAn lines are set to high impedance.

The following flags of IICA control register n0 (IICCTLn0) and the IICA status register n (IICSn) are

cleared to 0.

• STTn • SPTn • MSTSn • EXCn • COIn • TRCn • ACKDn • STDn

The standby mode following exit from communications remains in effect until the following communications entry

conditions are met.

• After a stop condition is detected, restart is in master mode.

• An address match or extension code reception occurs after the start condition.

Condition for clearing (LRELn = 0) Condition for setting (LRELn = 1)

• Automatically cleared after execution

• Reset

• Set by instruction

WRELn

Notes 2, 3

Wait cancellation

0 Do not cancel wait

1 Cancel wait. This setting is automatically cleared after wait is canceled.

When the WRELn bit is set (wait canceled) during the wait period at the ninth clock pulse in the transmission status

(TRCn = 1), the SDAAn line goes into the high impedance state (TRCn = 0).

Condition for clearing (WRELn = 0) Condition for setting (WRELn = 1)

• Automatically cleared after execution

• Reset

• Set by instruction

Loading...

Loading...