RL78/G1H CHAPTER 4 CPU ARCHITECTURE

R01UH0575EJ0120 Rev. 1.20 Page 61 of 920

Dec 22, 2016

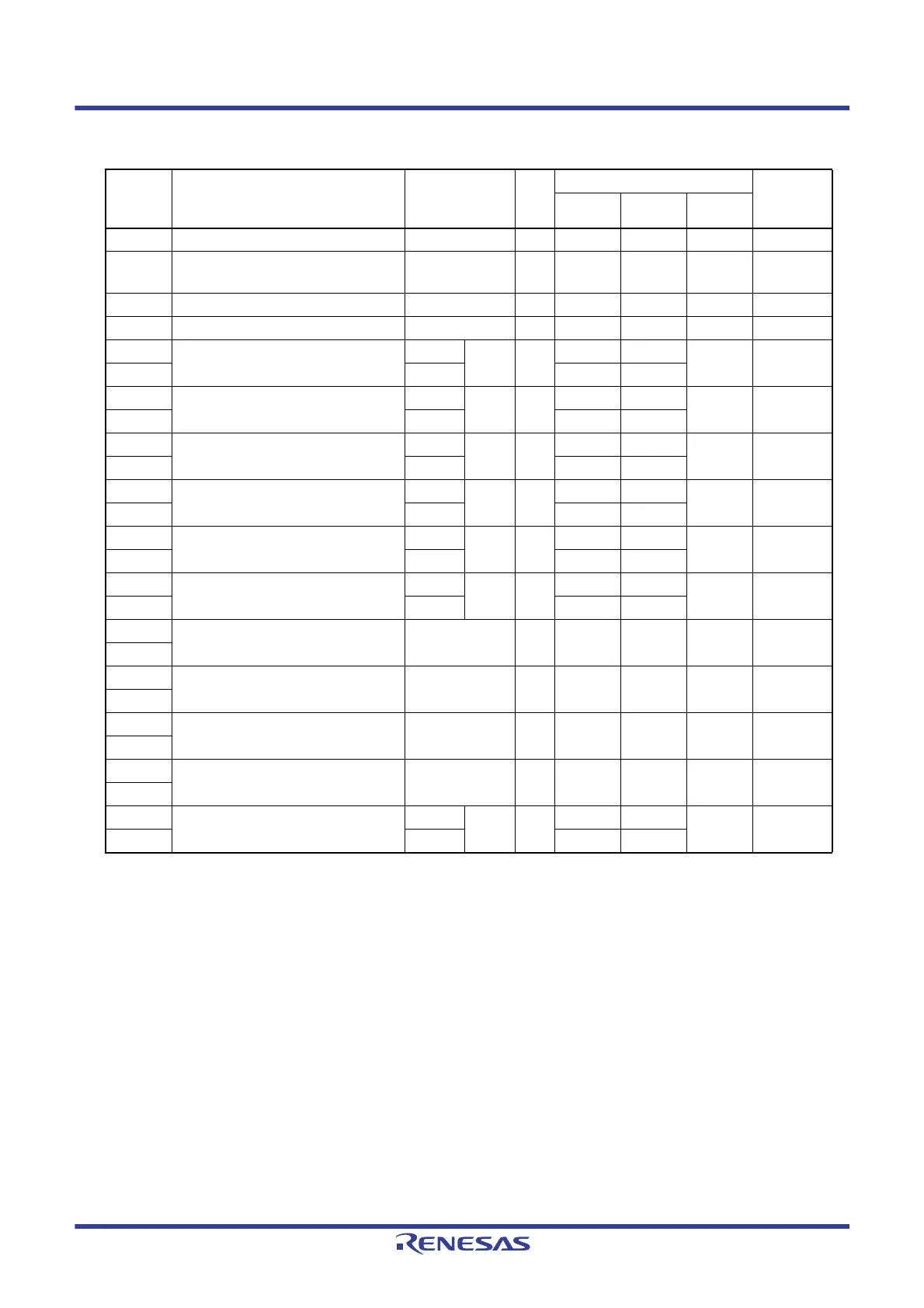

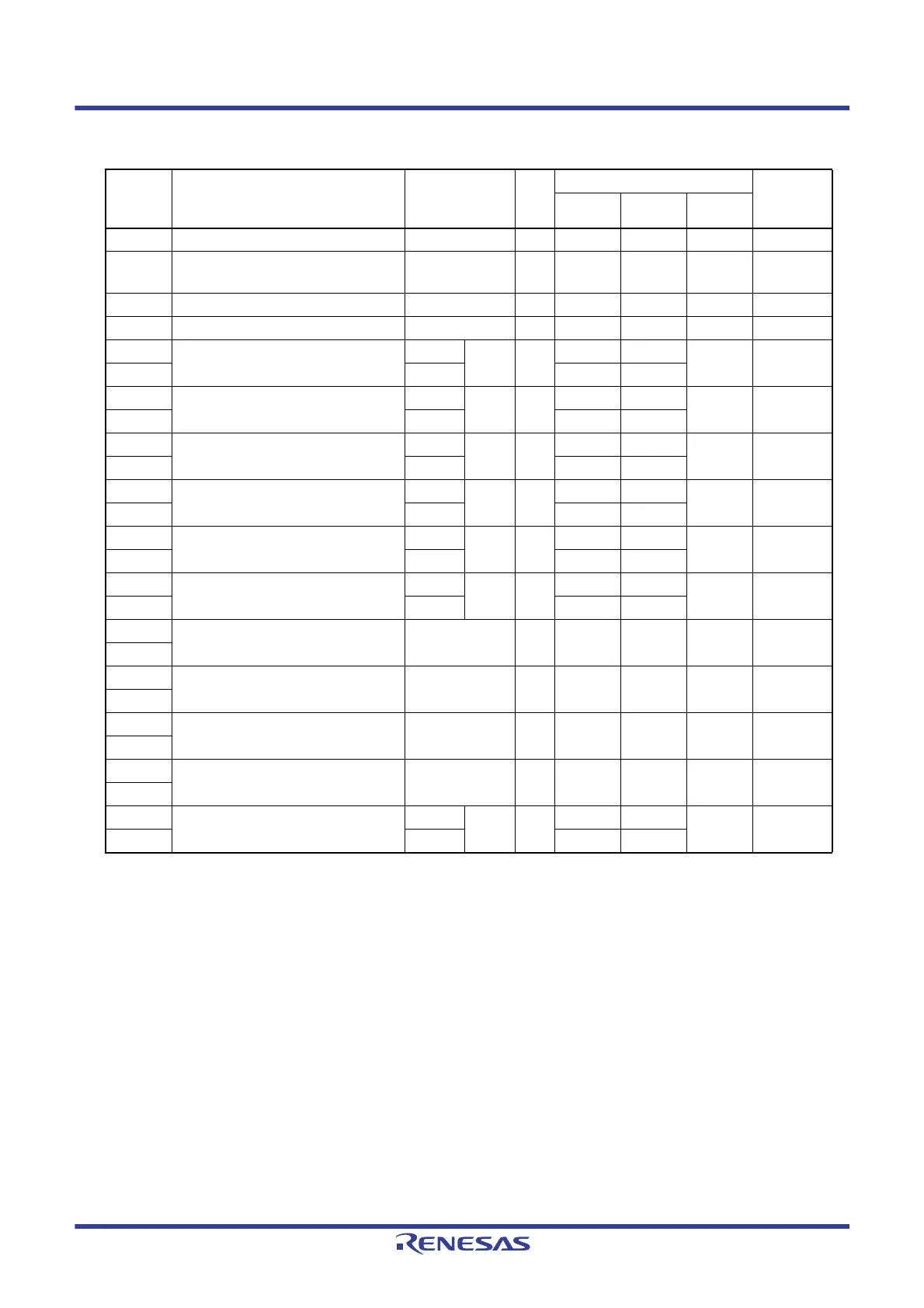

Table 4 - 11 Extended Special Function Register (2nd SFR) List (2/7)

Address

Extended Special Function Register

(2nd SFR) Name

Symbol R/W

Manipulable Bit Range

After Reset

1-bit 8-bit 16-bit

F00F0H Peripheral enable register 0 PER0 R/W

√√— 00H

F00F3H

Subsystem clock supply mode control

register

OSMC

R/W —

√ — 00H

F00F5H RAM parity error control register RPECTL R/W

√√— 00H

F00FEH BCD correction result register BCDADJ R —

√ — Undefined

F0104H Serial status register 02 SSR02L SSR02 R —

√√0000H

F0105H — — —

F0106H Serial status register 03 SSR03L SSR03 R —

√√0000H

F0107H — — —

F0108H Serial flag clear trigger register 00 SIR00L SIR00 R/W —

√√0000H

F0109H — — —

F010AH Serial flag clear trigger register 01 SIR01L SIR01 R/W —

√√0000H

F010BH — — —

F010CH Serial flag clear trigger register 02 SIR02L SIR02 R/W —

√√0000H

F010DH — — —

F010EH Serial flag clear trigger register 03 SIR03L SIR03 R/W —

√√0000H

F010FH — — —

F0114H Serial mode register 02 SMR02 R/W — —

√ 0020H

F0115H

F0116H Serial mode register 03 SMR03 R/W — —

√ 0020H

F0117H

F011CH Serial communication operation setting

register 02

SCR02 R/W — —

√ 0087H

F011DH

F011EH Serial communication operation setting

register 03

SCR03 R/W — —

√ 0087H

F011FH

F0120H Serial channel enable status register 0 SE0L SE0 R

√√√0000H

F0121H — — —

Loading...

Loading...