RL78/G1H CHAPTER 4 CPU ARCHITECTURE

R01UH0575EJ0120 Rev. 1.20 Page 66 of 920

Dec 22, 2016

Remark For SFRs in the SFR area, see Tables 4 - 5 to 4 - 9 SFR List.

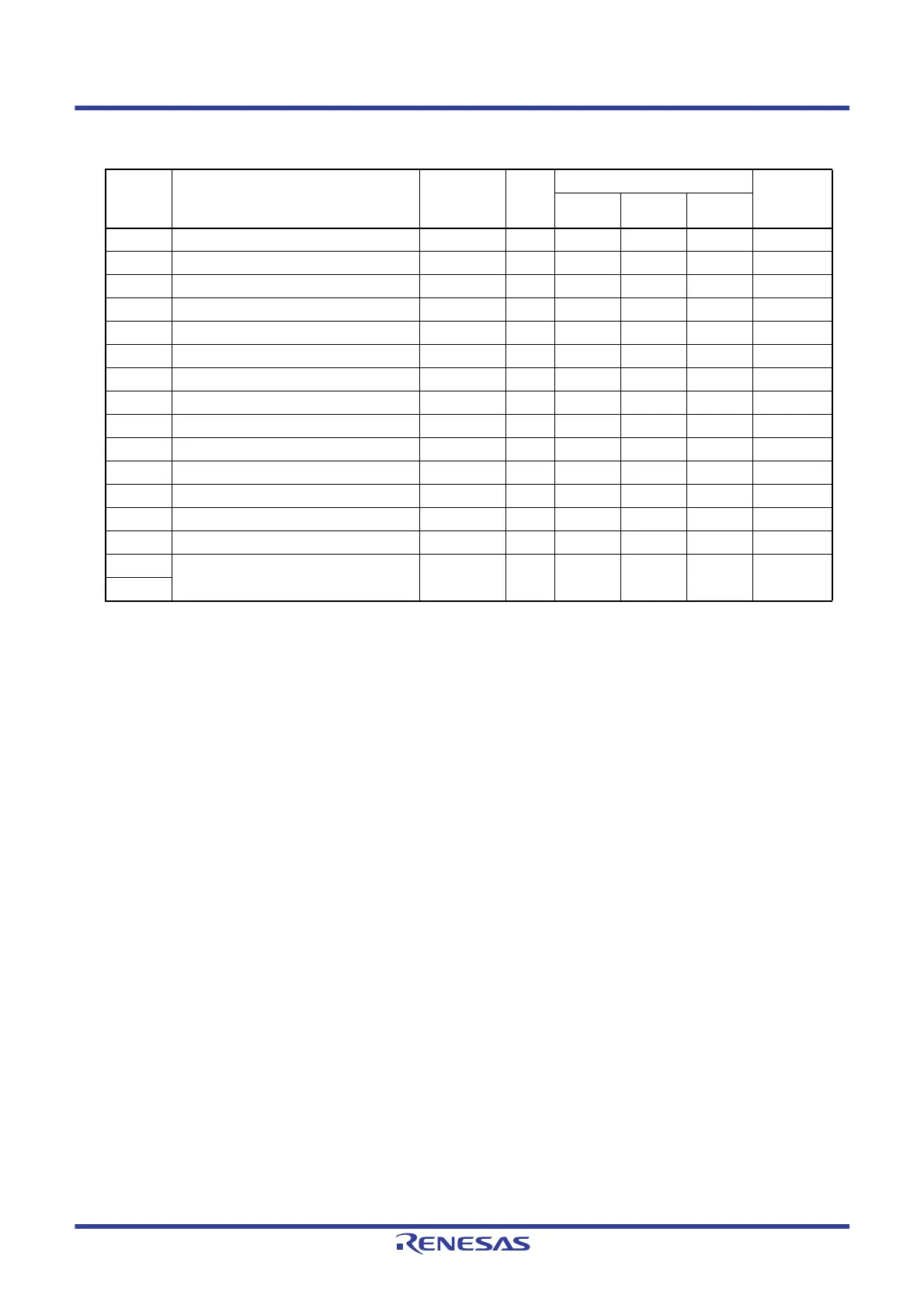

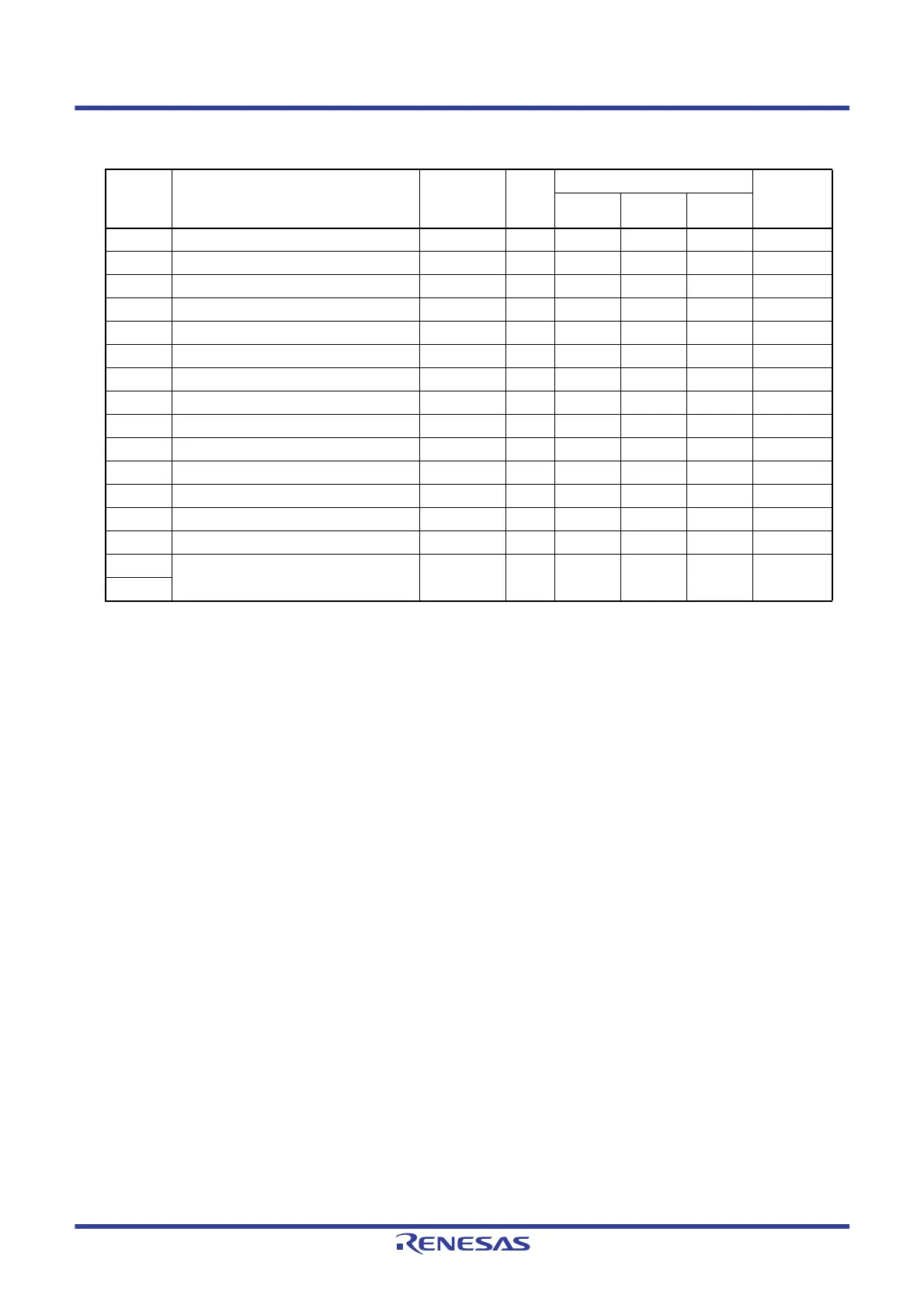

Table 4 - 16 Extended Special Function Register (2nd SFR) List (7/7)

Address

Extended Special Function Register

(2nd SFR) Name

Symbol R/W

Manipulable Bit Range

After Reset

1-bit 8-bit 16-bit

F02FAH CRC data register CRCD R/W — —

√ 0000H

F0300H Event output destination select register 00 ELSELR00 R/W —

√ — 00H

F0303H Event output destination select register 03 ELSELR03 R/W —

√ — 00H

F0304H Event output destination select register 04 ELSELR04 R/W —

√ — 00H

F0307H Event output destination select register 07 ELSELR07 R/W —

√ — 00H

F030DH Event output destination select register 13 ELSELR13 R/W —

√ — 00H

F0310H Event output destination select register 16 ELSELR16 R/W —

√ — 00H

F0311H Event output destination select register 17 ELSELR17 R/W —

√ — 00H

F0312H Event output destination select register 18 ELSELR18 R/W —

√ — 00H

F0313H Event output destination select register 19 ELSELR19 R/W —

√ — 00H

F0314H Event output destination select register 20 ELSELR20 R/W —

√ — 00H

F0315H Event output destination select register 21 ELSELR21 R/W —

√ — 00H

F0316H Event output destination select register 22 ELSELR22 R/W —

√ — 00H

F0317H Event output destination select register 23 ELSELR23 R/W —

√ — 00H

F0500H

Timer RJ counter register 0 TRJ0

R/W — —

√ FFFFH

F0501H

Loading...

Loading...