1 U8480 Series Remote Operation

56 U8480 Series Programming Guide

An example sequence

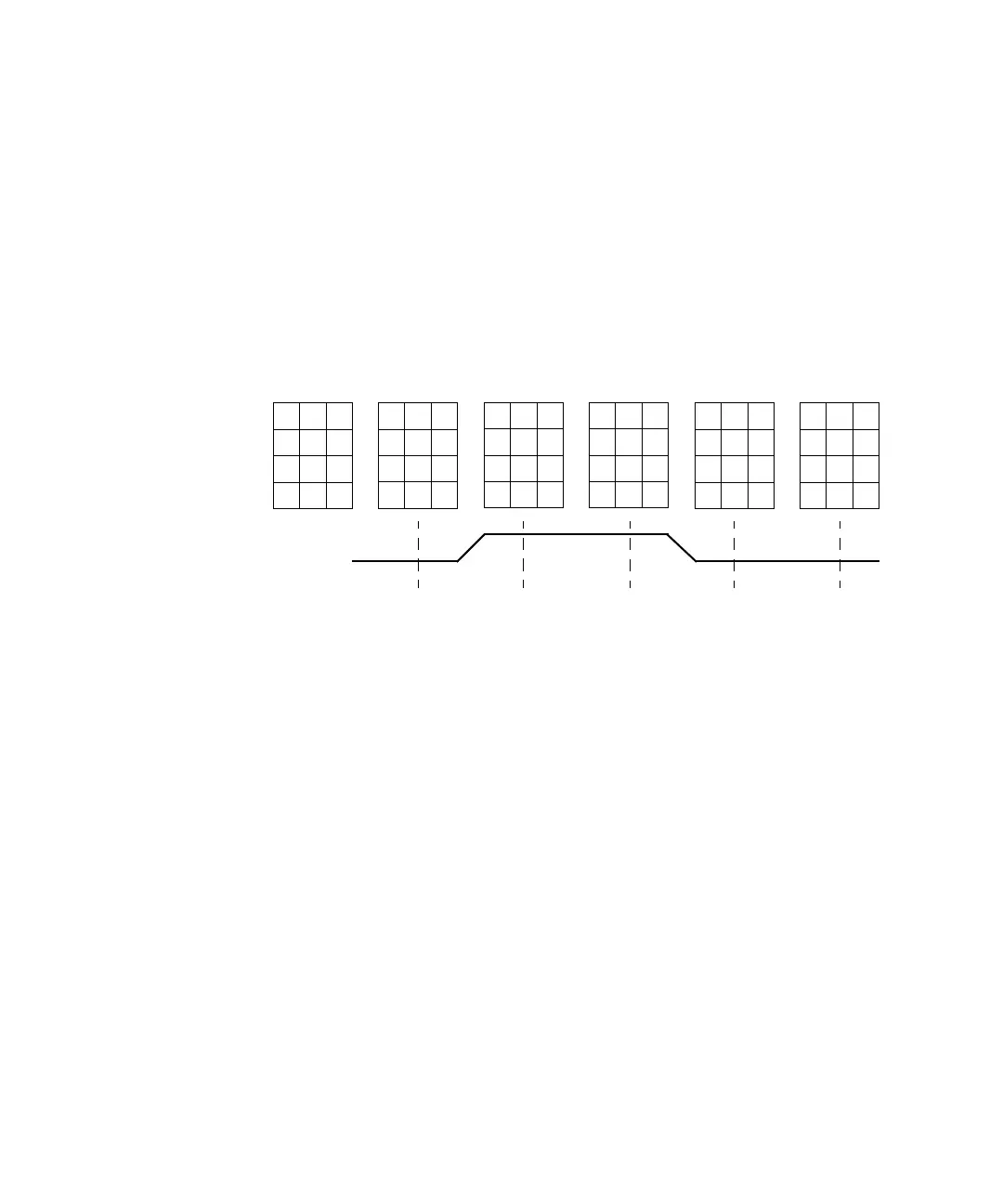

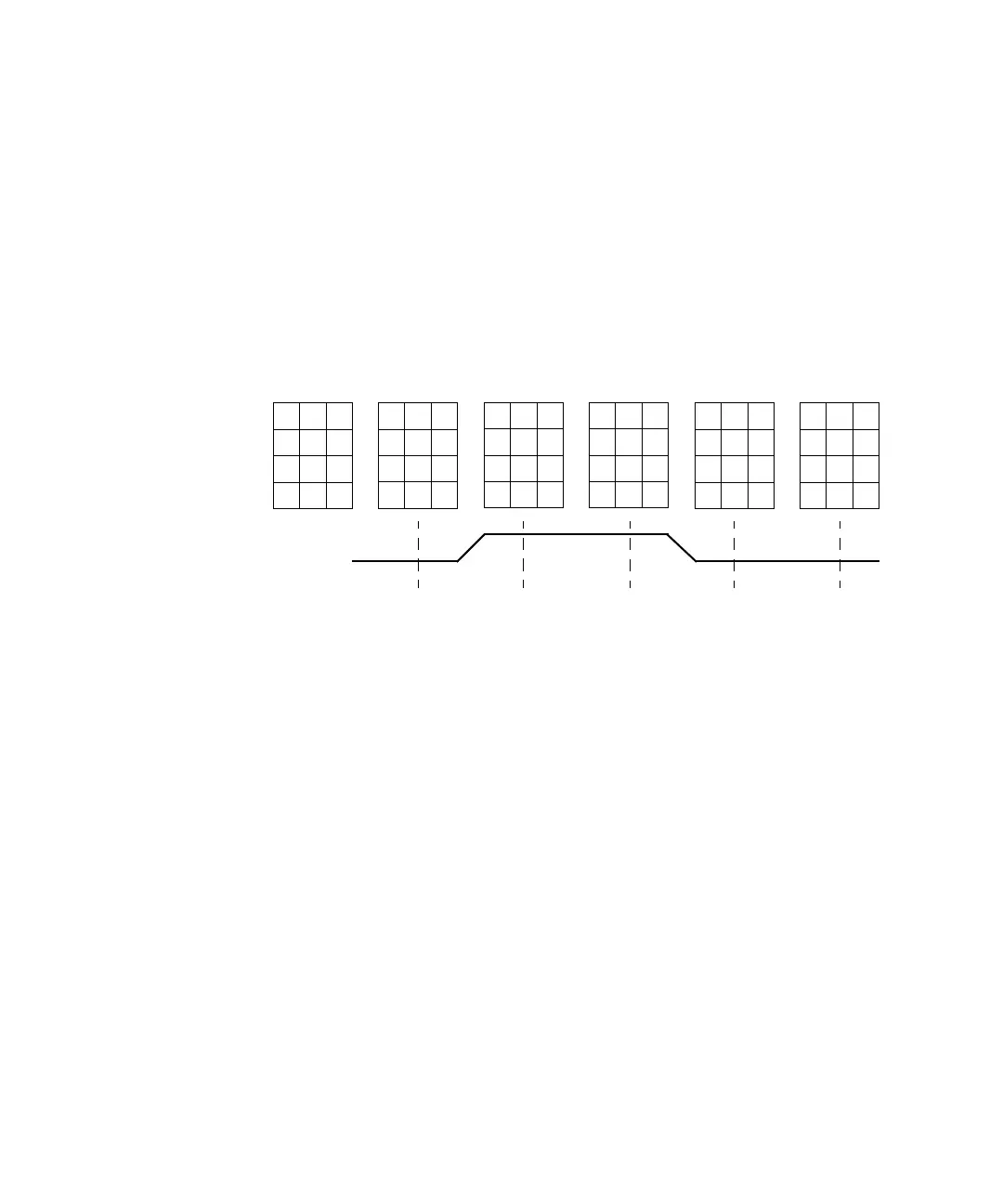

Figure 1-12 illustrates the response of a single bit position in a typical status

group for various settings. The changing state of the condition in question is

shown at the bottom of the figure. A small binary table shows the state of the

chosen bit in each status register at selected times T1 to T5.

Figure 1-12 Typical status register bit changes

Consider Case C, where the positive transition filter is set to 1 and negative

transition filter to 0. This configures the U8480 Series to set the corresponding bit

in the event register whenever the condition bit changes from 0 to 1. The enable

register is set to 1 to enable the summary bit to be generated each time there is a

change in the event register.

At time T1, the condition bit is 0. Since there is no changes to the condition bit at

this time, no corresponding bit in the event register will be set and the summary

bit is 0.

At time T2, the condition bit changes from 0 to 1. Since the positive transition filter

is set to detect condition bit changes from 0 to 1, the corresponding bit in the event

register will be set to 1. The enable register is set to 1, which means that the

summary bit will also be set to 1 whenever any bit in the event register is set to 1.

At time T3, the condition bit remains 1. The event register is cleared by a query.

Hence, the event register bit and summary bit are set to 0.

00

01

110

011

0

1

00

0

0

0

0

0

1

11

011

0

1

0

0

0

1

1

0

0

1

0

1

00

01

0

01

0

1

00

0

0

0

0

00

000

000

1

0

0

0

0

0

Case A

Case B

Case C

Case D

Condition

PTR

NTR

Enable

Condition

Event

Summary Bit

Condition

Event

Summary Bit

Condition

Event

Summary Bit

Condition

Event

Summary Bit

Condition

Event

Summary Bit

1

0

T1 T2 T3

T4

T5

00

0

0

00

***

*

marks when the event register is read

Loading...

Loading...