dsPIC30F Family Reference Manual

DS70068C-page 21-22 © 2004 Microchip Technology Inc.

21.5.5 Generating Stop Bus Event

Setting the Stop sequence enable bit, PEN (I2CCON<2>), enables generation of a master Stop

sequence.

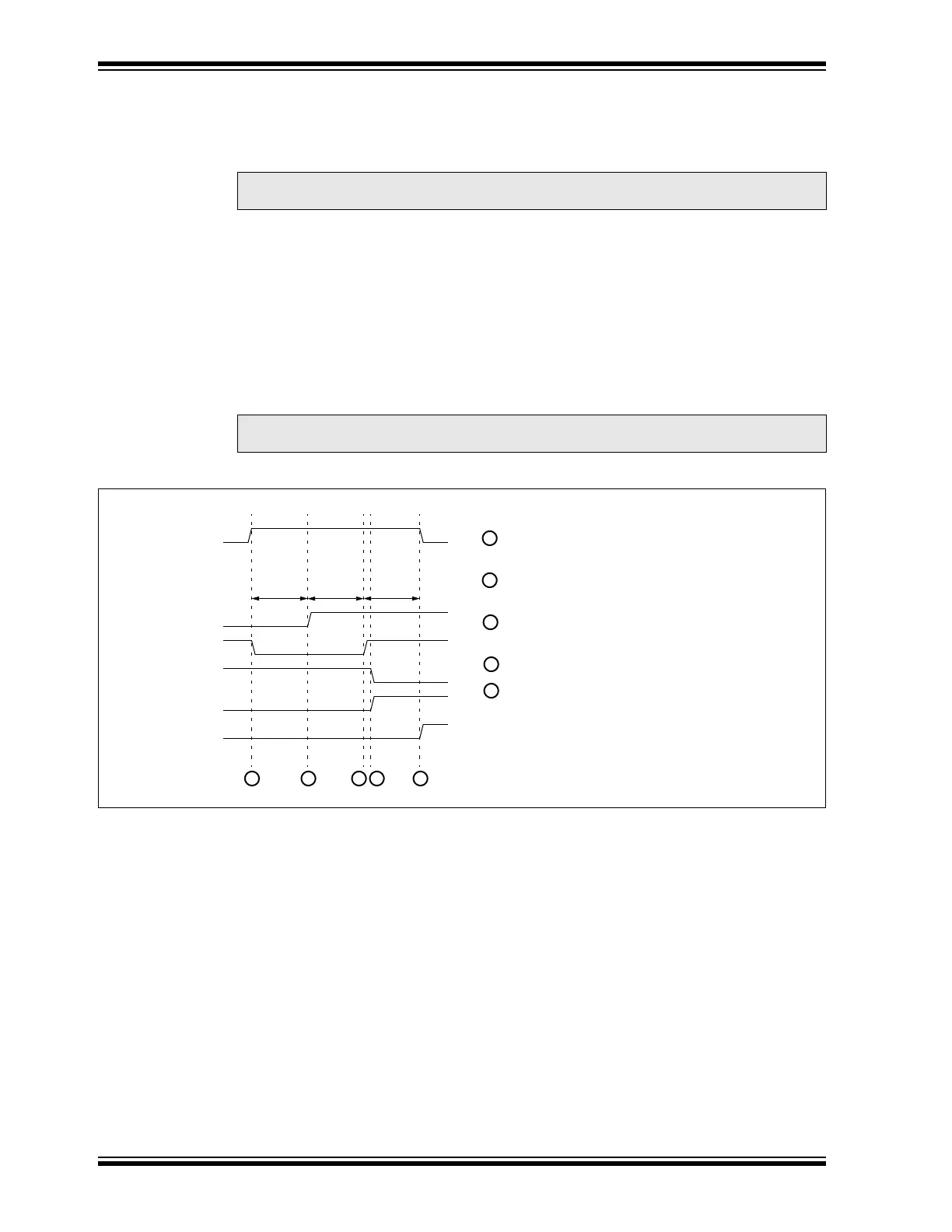

When the PEN bit is set, the master generates the Stop sequence as shown in Figure 21-13.

• The slave detects the Stop condition, sets the P bit (I2CSTAT<4>) and clears the S bit

(I2CSTAT<3>).

• The PEN bit is automatically cleared.

• The module generates the MI2CIF interrupt.

21.5.5.1 IWCOL Status Flag

If the software writes the I2CTRN when a Stop sequence is in progress, then the IWCOL bit is

set and the contents of the buffer are unchanged (the write doesn’t occur).

Figure 21-13: Master Stop Timing Diagram

Note: The lower 5 bits of I2CCON must be ‘0’ (master logic inactive) before attempting to

set the PEN bit.

Note: Because queueing of events is not allowed, writing to the lower 5 bits of I2CCON is

disabled until the Stop condition is complete.

SCL (Master)

SDA (Master)

S

PEN

MI2CIF Interrupt

TBRG

1 2 3 5

- Writing PEN = 1 initiates a master Stop event.

1

TBRG

Baud generator starts. Module drives SDA low.

- Baud generator times out. Module releases SCL.

2

Baud generator restarts.

- Baud generator times out. Module releases SDA.

3

- Slave logic detects Stop. Module sets P = 1, S = 0.

4

I

2

C Bus State

(P) (I)

P

TBRG

(Q)

4

Baud generator restarts.

- The baud generator times out. Module clears PEN.

5

Master generates interrupt.

(Q)

Loading...

Loading...