G.12

SEL-351A Relay Instruction Manual Date Code 20080213

Setting SELOGIC Control Equations

Processing Order and Processing Interval

Processing Order and Processing Interval

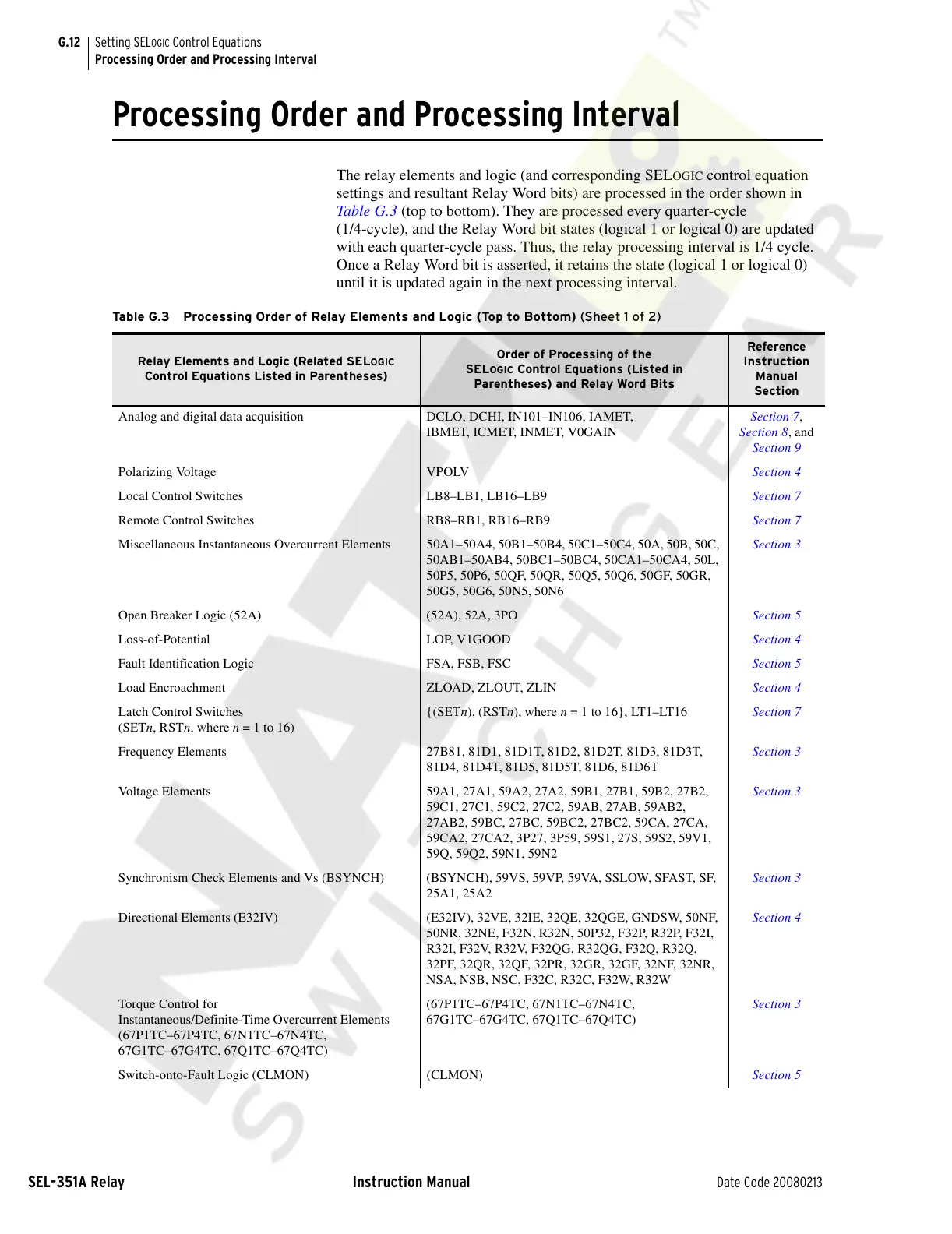

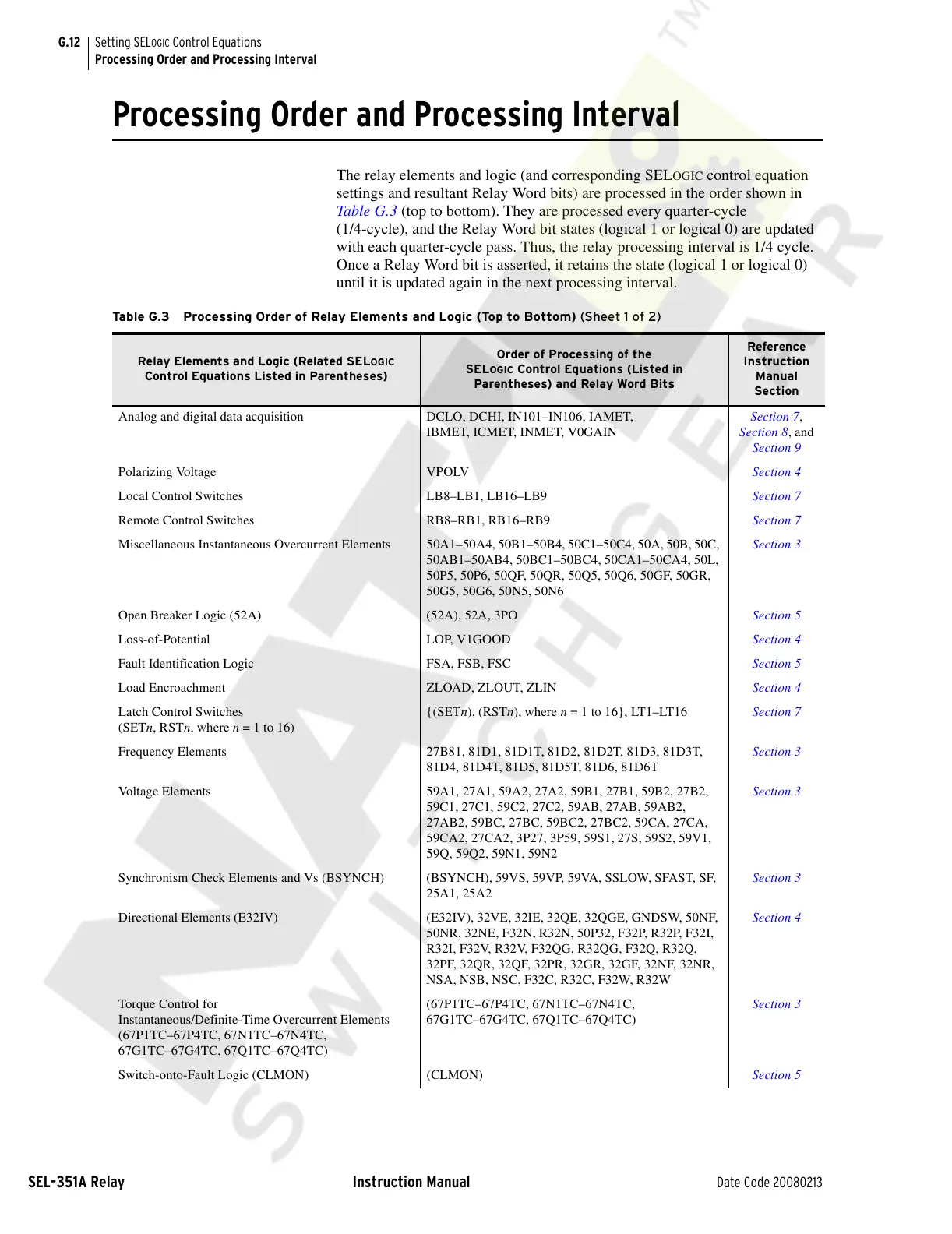

The relay elements and logic (and corresponding SELOGIC control equation

settings and resultant Relay Word bits) are processed in the order shown in

Table G.3 (top to bottom). They are processed every quarter-cycle

(1/4-cycle), and the Relay Word bit states (logical 1 or logical 0) are updated

with each quarter-cycle pass. Thus, the relay processing interval is 1/4 cycle.

Once a Relay Word bit is asserted, it retains the state (logical 1 or logical 0)

until it is updated again in the next processing interval.

Table G.3 Processing Order of Relay Elements and Logic (Top to Bottom) (Sheet 1 of 2)

Relay Elements and Logic (Related SELOGIC

Control Equations Listed in Parentheses)

Order of Processing of the

SEL

OGIC Control Equations (Listed in

Parentheses) and Relay Word Bits

Reference

Instruction

Manual

Section

Analog and digital data acquisition DCLO, DCHI, IN101–IN106, IAMET,

IBMET, ICMET, INMET, V0GAIN

Section 7,

Section 8, and

Section 9

Polarizing Voltage VPOLV Section 4

Local Control Switches LB8–LB1, LB16–LB9 Section 7

Remote Control Switches RB8–RB1, RB16–RB9 Section 7

Miscellaneous Instantaneous Overcurrent Elements 50A1–50A4, 50B1–50B4, 50C1–50C4, 50A, 50B, 50C,

50AB1–50AB4, 50BC1–50BC4, 50CA1–50CA4, 50L,

50P5, 50P6, 50QF, 50QR, 50Q5, 50Q6, 50GF, 50GR,

50G5, 50G6, 50N5, 50N6

Section 3

Open Breaker Logic (52A) (52A), 52A, 3PO Section 5

Loss-of-Potential LOP, V1GOOD Section 4

Fault Identification Logic FSA, FSB, FSC Section 5

Load Encroachment ZLOAD, ZLOUT, ZLIN Section 4

Latch Control Switches

(SETn, RSTn, where n = 1 to 16)

{(SETn), (RSTn), where n = 1 to 16}, LT1–LT16 Section 7

Frequency Elements 27B81, 81D1, 81D1T, 81D2, 81D2T, 81D3, 81D3T,

81D4, 81D4T, 81D5, 81D5T, 81D6, 81D6T

Section 3

Voltage Elements 59A1, 27A1, 59A2, 27A2, 59B1, 27B1, 59B2, 27B2,

59C1, 27C1, 59C2, 27C2, 59AB, 27AB, 59AB2,

27AB2, 59BC, 27BC, 59BC2, 27BC2, 59CA, 27CA,

59CA2, 27CA2, 3P27, 3P59, 59S1, 27S, 59S2, 59V1,

59Q, 59Q2, 59N1, 59N2

Section 3

Synchronism Check Elements and Vs (BSYNCH) (BSYNCH), 59VS, 59VP, 59VA, SSLOW, SFAST, SF,

25A1, 25A2

Section 3

Directional Elements (E32IV) (E32IV), 32VE, 32IE, 32QE, 32QGE, GNDSW, 50NF,

50NR, 32NE, F32N, R32N, 50P32, F32P, R32P, F32I,

R32I, F32V, R32V, F32QG, R32QG, F32Q, R32Q,

32PF, 32QR, 32QF, 32PR, 32GR, 32GF, 32NF, 32NR,

NSA, NSB, NSC, F32C, R32C, F32W, R32W

Section 4

Torque Control for

Instantaneous/Definite-Time Overcurrent Elements

(67P1TC–67P4TC, 67N1TC–67N4TC,

67G1TC–67G4TC, 67Q1TC–67Q4TC)

(67P1TC–67P4TC, 67N1TC–67N4TC,

67G1TC–67G4TC, 67Q1TC–67Q4TC)

Section 3

Switch-onto-Fault Logic (CLMON) (CLMON) Section 5

Courtesy of NationalSwitchgear.com

Loading...

Loading...