L.5

Date Code 20080213 Instruction Manual SEL-351A Relay

SEL Synchrophasors

Protocol Operation

Protocol Operation

SEL Fast Message Unsolicited Write (synchrophasor) messages are general

Fast Messages (A546h) that transport measured synchrophasor information.

Transmit Mode

Control

The SEL-351A begins transmitting synchrophasors when an enable message

is received from the connected device. The relay stops synchrophasor

transmission on a particular serial port when the disable command is received

from the connected device, or when the relay settings are changed. The

SEL-351A responds to configuration block request messages regardless of the

present transmit status, waiting only as long as it takes for any partially sent

messages to be completely transmitted.

Table L.1–Table L.3 list the Synchrophasor Fast Message protocol formats,

including the specific construction of the enable and disable messages. SEL

Application Guide AG2002-08 provides additional information on the SEL

Fast Message Synchrophasor protocol and example applications. This

application guide refers to the SEL-421 Relay and differs slightly from the

SEL-351A implementation.

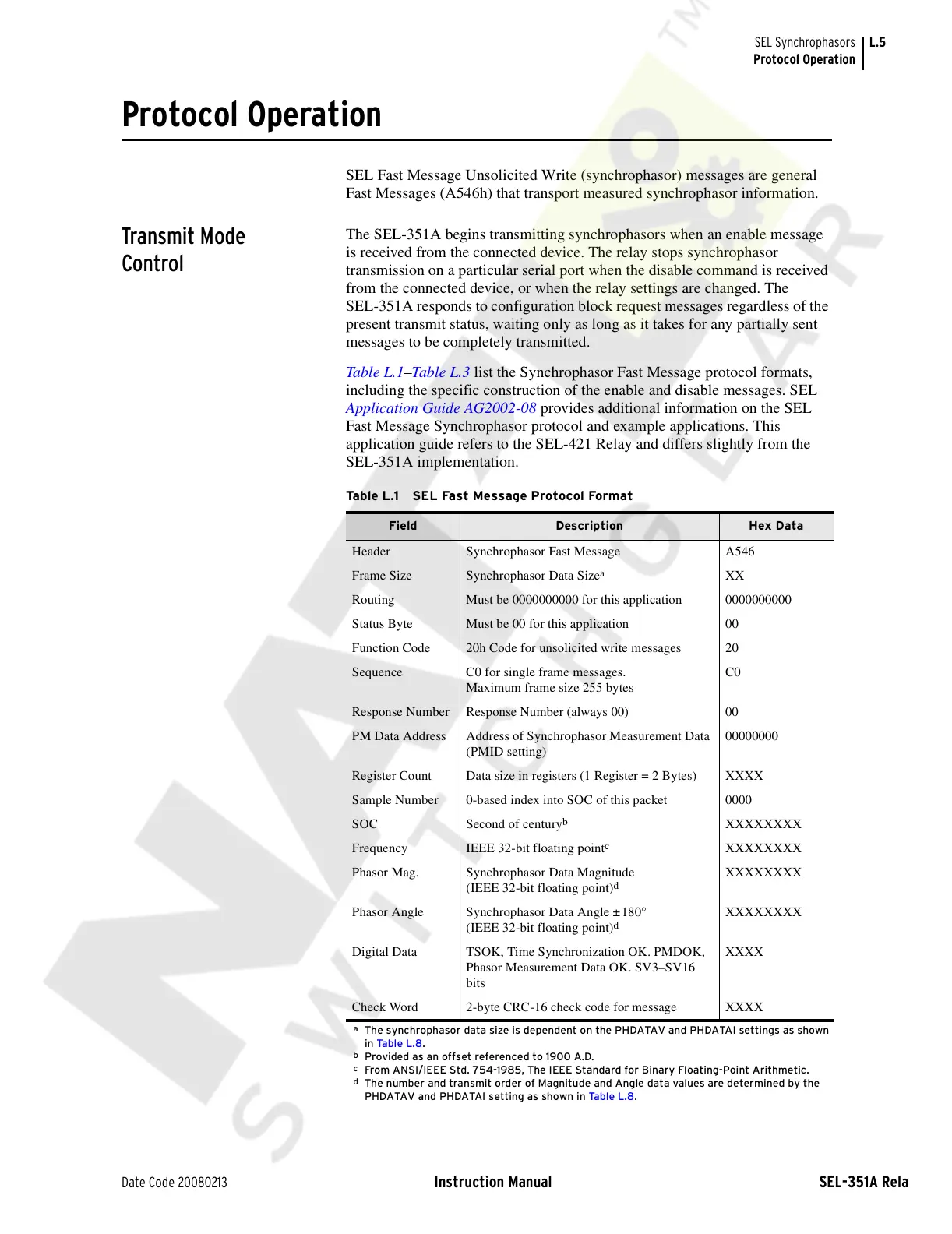

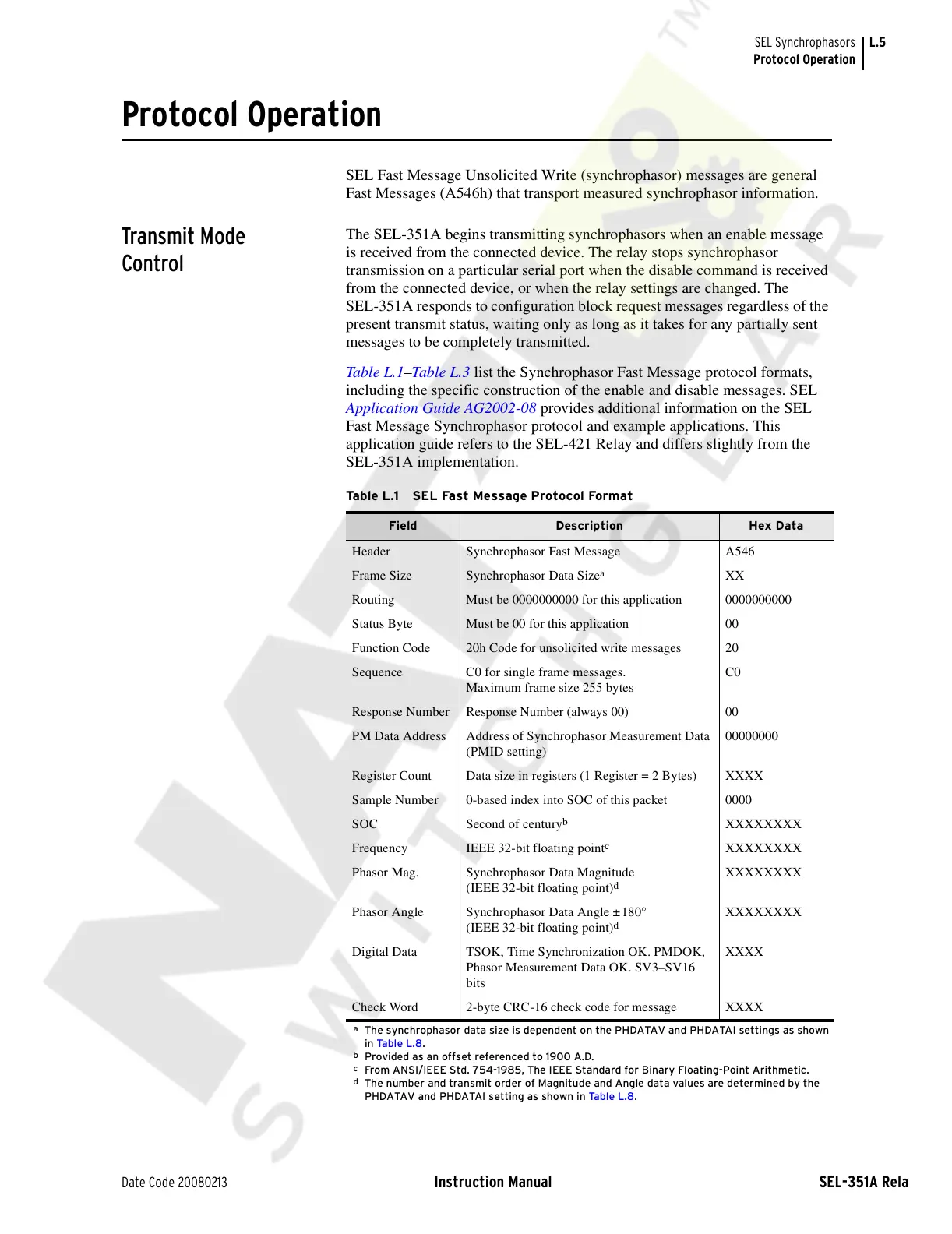

Table L.1 SEL Fast Message Protocol Format

Field Description Hex Data

Header Synchrophasor Fast Message A546

Frame Size Synchrophasor Data Size

a

a

The synchrophasor data size is dependent on the PHDATAV and PHDATAI settings as shown

in Ta b l e L . 8 .

XX

Routing Must be 0000000000 for this application 0000000000

Status Byte Must be 00 for this application 00

Function Code 20h Code for unsolicited write messages 20

Sequence C0 for single frame messages.

Maximum frame size 255 bytes

C0

Response Number Response Number (always 00) 00

PM Data Address Address of Synchrophasor Measurement Data

(PMID setting)

00000000

Register Count Data size in registers (1 Register = 2 Bytes) XXXX

Sample Number 0-based index into SOC of this packet 0000

SOC Second of century

b

b

Provided as an offset referenced to 1900 A.D.

XXXXXXXX

Frequency IEEE 32-bit floating point

c

c

From ANSI/IEEE Std. 754-1985, The IEEE Standard for Binary Floating-Point Arithmetic.

XXXXXXXX

Phasor Mag. Synchrophasor Data Magnitude

(IEEE 32-bit floating point)

d

d

The number and transmit order of Magnitude and Angle data values are determined by the

PHDATAV and PHDATAI setting as shown in Ta b le L . 8.

XXXXXXXX

Phasor Angle Synchrophasor Data Angle ±180°

(IEEE 32-bit floating point)

d

XXXXXXXX

Digital Data TSOK, Time Synchronization OK. PMDOK,

Phasor Measurement Data OK. SV3–SV16

bits

XXXX

Check Word 2-byte CRC-16 check code for message XXXX

Courtesy of NationalSwitchgear.com

Loading...

Loading...