General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0440

1286/2126 RM0440 Rev 4

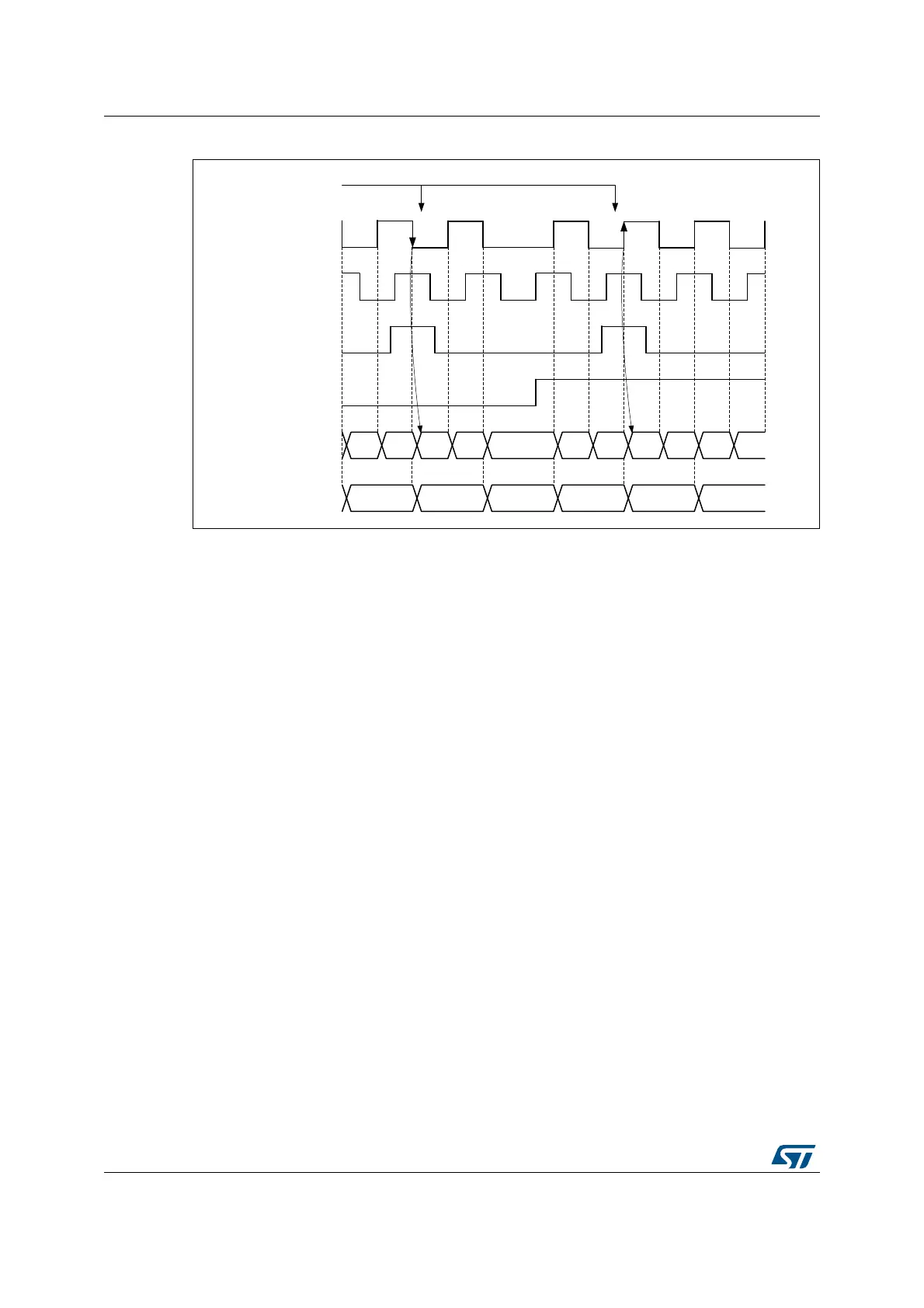

Figure 419. Index behavior in x1 and x2 mode (IPOS[1:0] = 01)

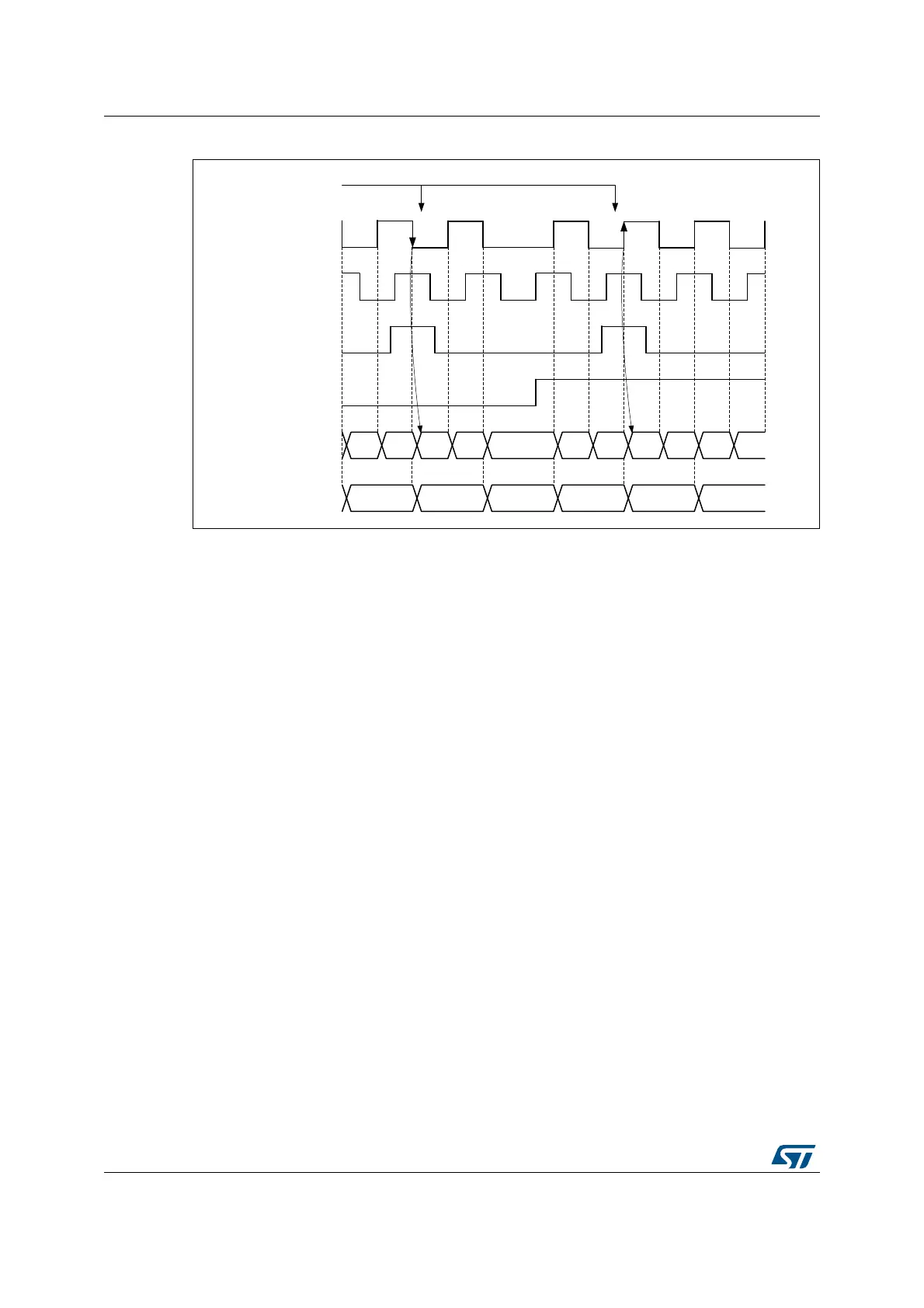

Directional index sensitivity

The IDIR[1:0] bitfield in the TIMx_ECR register allows the index to be active only in a

selected counting direction.

The Figure 420 below shows the relationship between index and counter reset events,

depending on IDIR[1:0] value.

Note: The IDR[1:0] bitfield must be written when IE bit is reset (index mode disabled).

Note: The directional index sensitivity is not supported in clock + direction mode. When

SMS[3:0] = 1010 or 1011, the IDIR[1:0] must be set to 00.

MSv45773V1

Channel A

Channel B

DIR bit

Index

Counter x1

5 6 7 0 1

3

Counter x2 10 11 0 1 2 1 0 11 10 9 8

AB = IPOS[1:0] = 01

Loading...

Loading...