General-purpose timers (TIM15/TIM16/TIM17) RM0440

1358/2126 RM0440 Rev 4

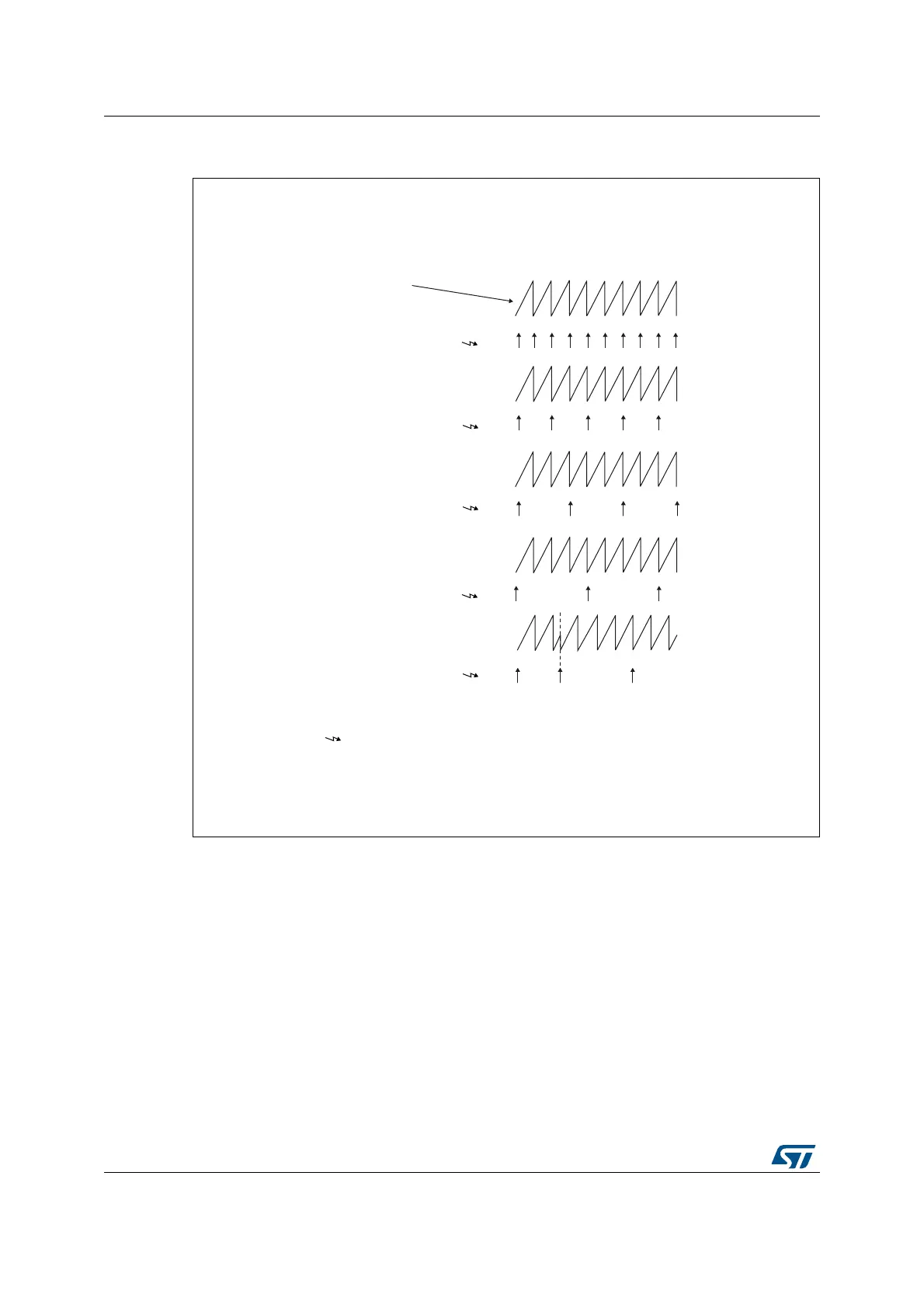

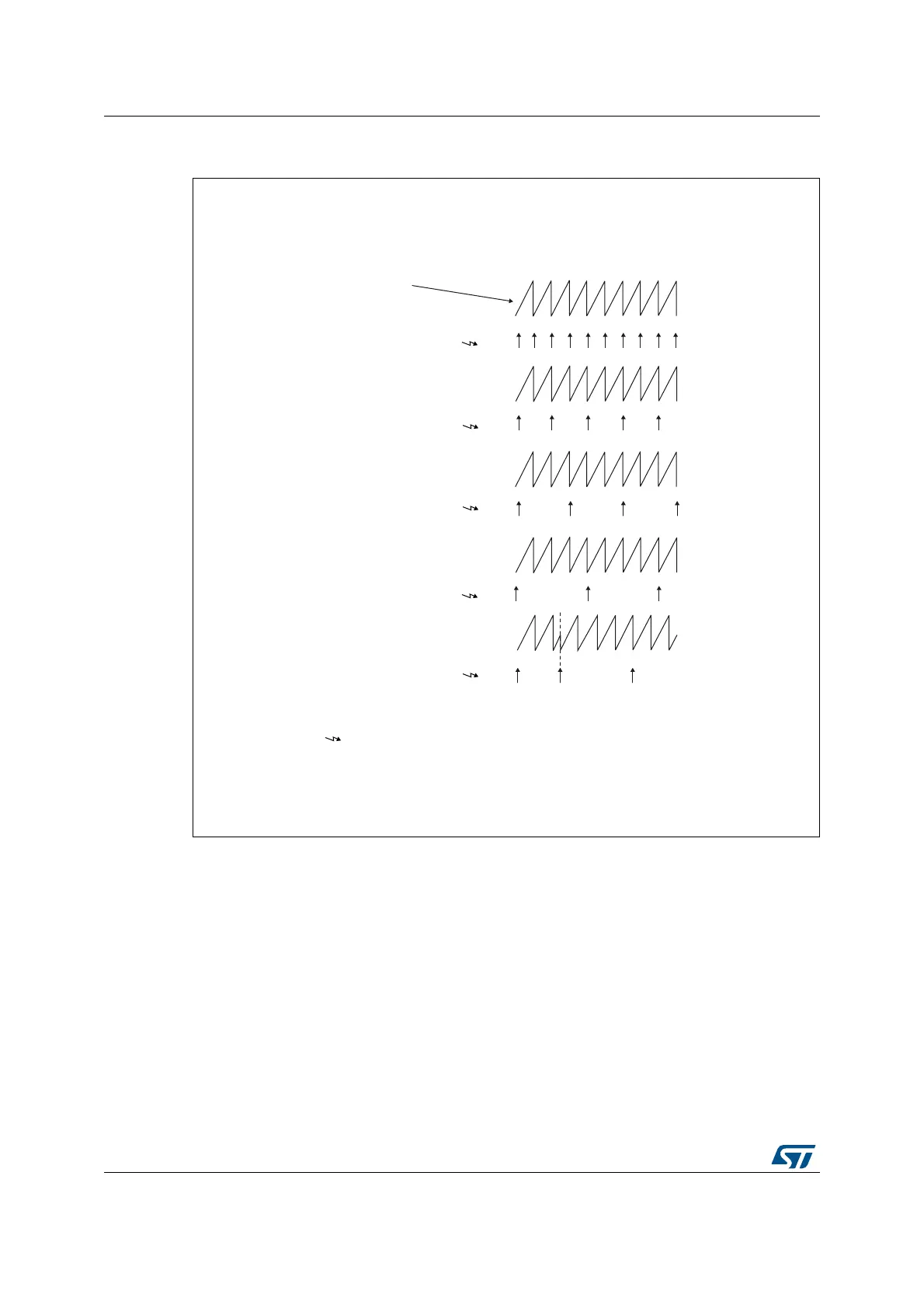

Figure 449. Update rate examples depending on mode and TIMx_RCR register

settings

30.4.6 Clock selection

The counter clock can be provided by the following clock sources:

• Internal clock (tim_ker_ck)

• External clock mode1: external input pin (tim_ti1 or tim_ti2, if available)

• Internal trigger inputs (tim_itrx) (only for TIM15): using one timer as the prescaler for

another timer, for example, TIM1 can be configured to act as a prescaler for TIM15.

Refer to Using one timer to enable another timer for more details.

Internal clock source (tim_ker_ck)

If the slave mode controller is disabled (SMS=000), then the CEN (in the TIMx_CR1

register) and UG bits (in the TIMx_EGR register) are actual control bits and can be changed

Edge-aligned mode

UEV

Update Event: preload registers transferred to active registers

and update interrupt generated.

Counter

TIMx_CNT

TIMx_RCR = 0 UEV

TIMx_RCR = 1 UEV

TIMx_RCR = 2 UEV

TIMx_RCR = 3 UEV

TIMx_RCR = 3

and

re-synchronization UEV

(by SW)

Upcounting

MS31084V2

Loading...

Loading...