Basic timers (TIM6/TIM7) RM0440

1454/2126 RM0440 Rev 4

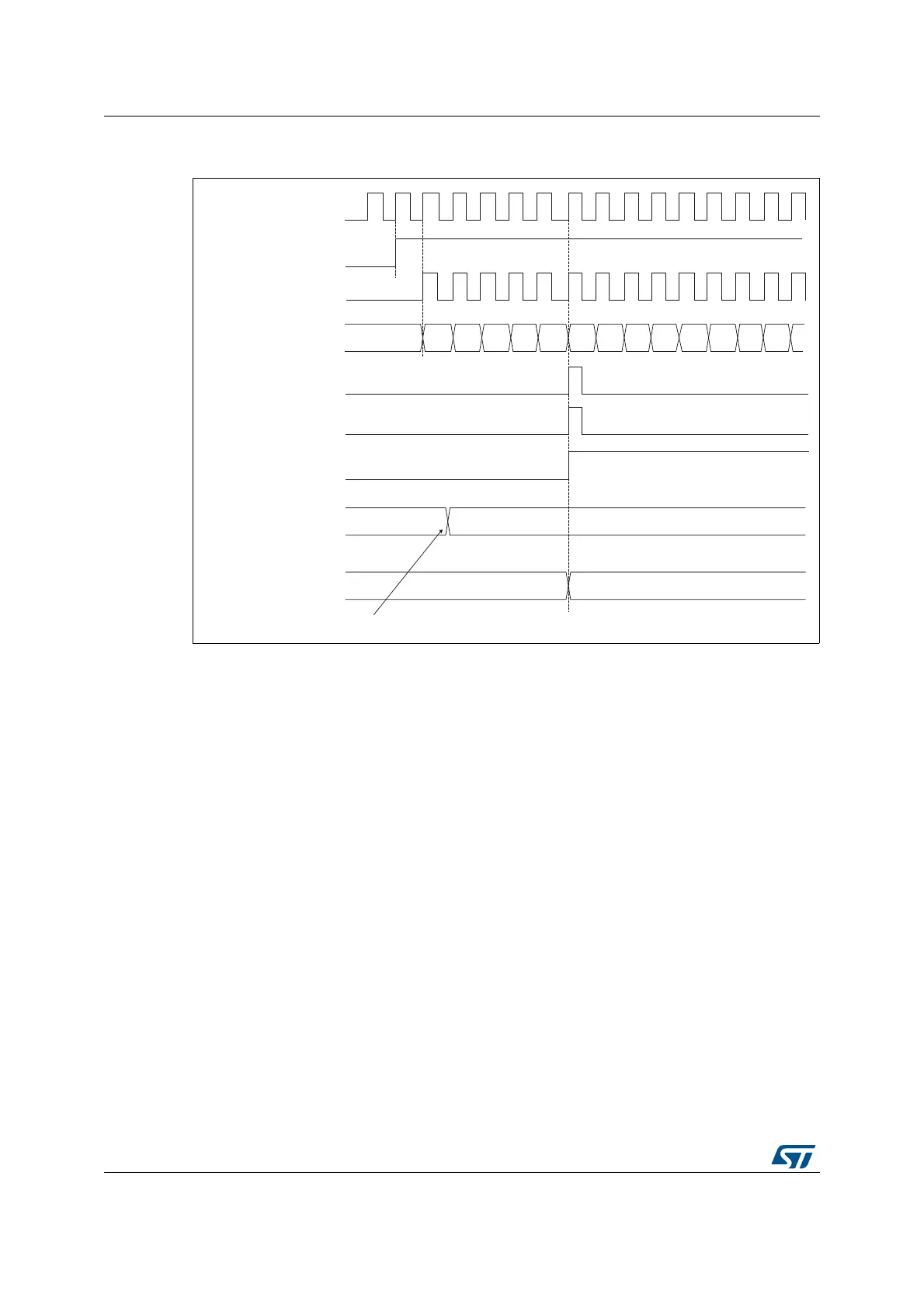

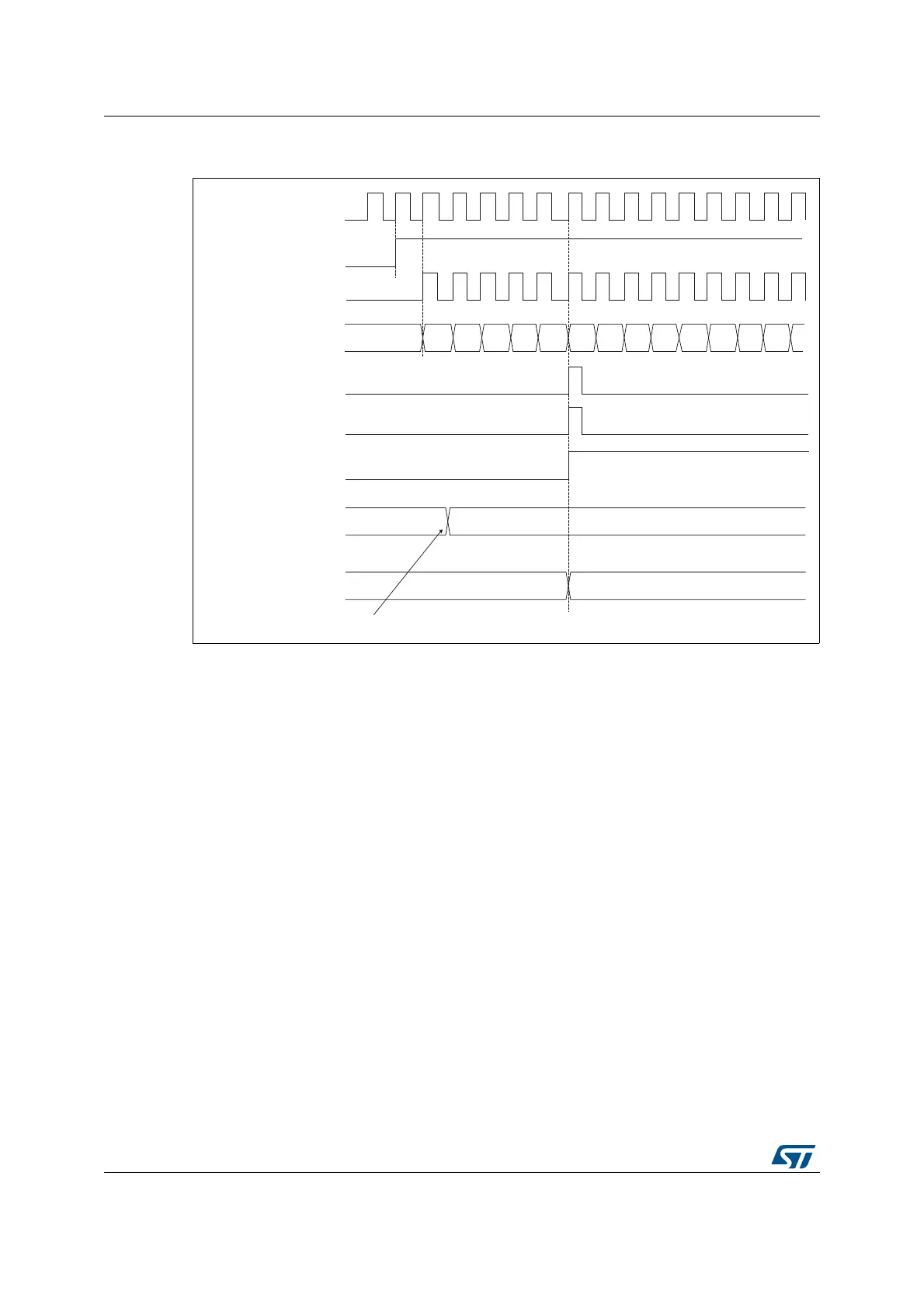

Figure 488. Counter timing diagram, update event when ARPE=1 (TIMx_ARR

preloaded)

Dithering mode

The time base effective resolution can be increased by enabling the dithering mode, using

the DITHEN bit in the TIMx_CR1 register. This affects the way the TIMx_ARR is behaving,

and is useful for adjusting the average counter period when the timer is used as a trigger

(typically for a DAC).

The operating principle is to have the actual ARR value slightly changed (adding or not one

timer clock period) over 16 consecutive counting periods, with predefined patterns. This

allows a 16-fold resolution increase, considering the average counting period.

The Figure 489 below presents the dithering principle applied to 4 consecutive counting

periods.

MSv62304V1

F5

36

tim_psc_ck

tim_cnt_ck

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag

(UIF)

00

02

03 04 05

06

07F1

F2

F3 F4

F5F0

01

CEN

Auto-reload preload

register

Write a new value in TIMx_ARR

Auto-reload shadow

register

F5

36

Loading...

Loading...