Low-power universal asynchronous receiver transmitter (LPUART) RM0440

1686/2126 RM0440 Rev 4

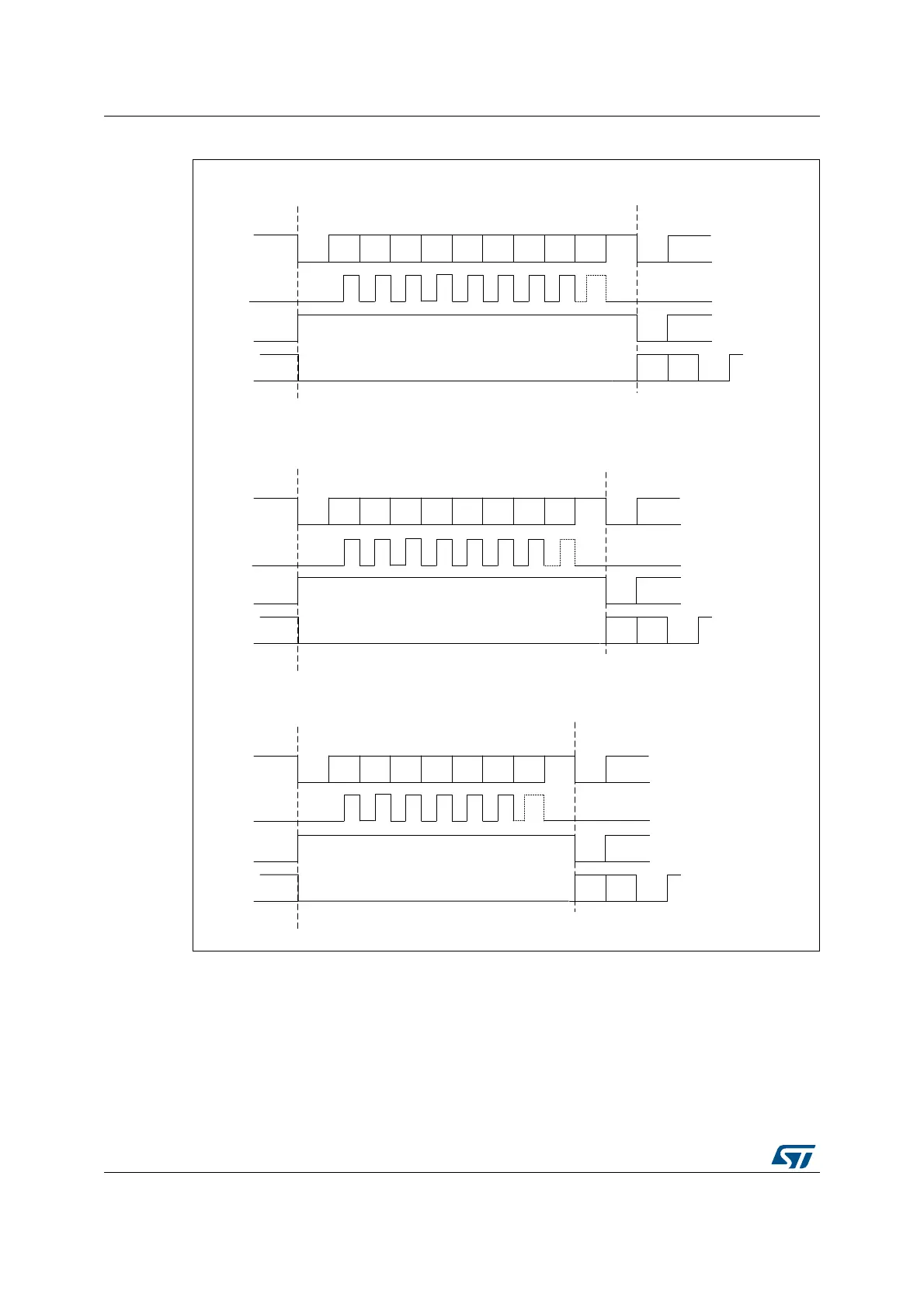

Figure 558. LPUART word length programming

38.4.4 LPUART FIFOs and thresholds

The LPUART can operate in FIFO mode.

The LPUART comes with a Transmit FIFO (TXFIFO) and a Receive FIFO (RXFIFO). The

FIFO mode is enabled by setting FIFOEN bit (bit 29) in LPUART_CR1 register.

Since 9 bits the maximum data word length is 9 bits, the TXFIFO is 9-bits wide. However the

RXFIFO default width is 12 bits. This is due to the fact that the receiver does not only store

MS33194V2

Bit0 Bit1 Bit2 Bit3 Bit4 Bit5 Bit6 Bit7 Bit8

Start

bit

Stop

bit

Next

Start

bit

Idle frame

9-bit word length (M = 01 ), 1 Stop bit

Possible

Parity

bit

Break frame

Data frame

Clock **

Start

bit

Stop

bit

Start

bit

Stop

bit

Bit0 Bit1 Bit2 Bit3 Bit4 Bit5 Bit6 Bit7

Start

bit

Stop

bit

Next

Start

bit

Idle frame

8-bit word length (M = 00 ), 1 Stop bit

Possible

Parity

bit

Break frame

Data frame

Clock **

Start

bit

Stop

bit

Start

bit

Stop

bit

Bit0 Bit1 Bit2 Bit3 Bit4 Bit5 Bit6

Start

bit

Stop

bit

Next

Start

bit

Idle frame

7-bit word length (M = 10 ), 1 Stop bit

Possible

Parity

bit

Break frame

Data frame

Clock

** LBCL bit controls last data clock pulse

**

Start

bit

Stop

bit

Start

bit

Stop

bit

Loading...

Loading...