RM0440 Rev 4 247/2126

RM0440 Power control (PWR)

271

6.3.6 Stop 0 mode

The Stop 0 mode is based on the Cortex

®

-M4 with FPU deepsleep mode combined with the

peripheral clock gating. The voltage regulator is configured in main regulator mode. In Stop

0 mode, all clocks in the V

CORE

domain are stopped; the PLL, the HSI16 and the HSE

oscillators are disabled. Some peripherals with the wakeup capability (I2Cx (x=1,2,3,4),

U(S)ARTx(x=1,2...5) and LPUART) can switch on the HSI16 to receive a frame, and switch

off the HSI16 after receiving the frame if it is not a wakeup frame. In this case, the HSI16

clock is propagated only to the peripheral requesting it.

SRAM1, SRAM2, CCM SRAM and register contents are preserved.

The BOR is always available in Stop 0 mode. The consumption is increased when

thresholds higher than V

BOR0

are used.

I/O states in Stop 0 mode

In the Stop 0 mode, all I/O pins keep the same state as in the Run mode.

Entering the Stop 0 mode

The Stop 0 mode is entered according Section : Entering low power mode, when the

SLEEPDEEP bit in the Cortex

®

-M4 with FPU System Control register is set.

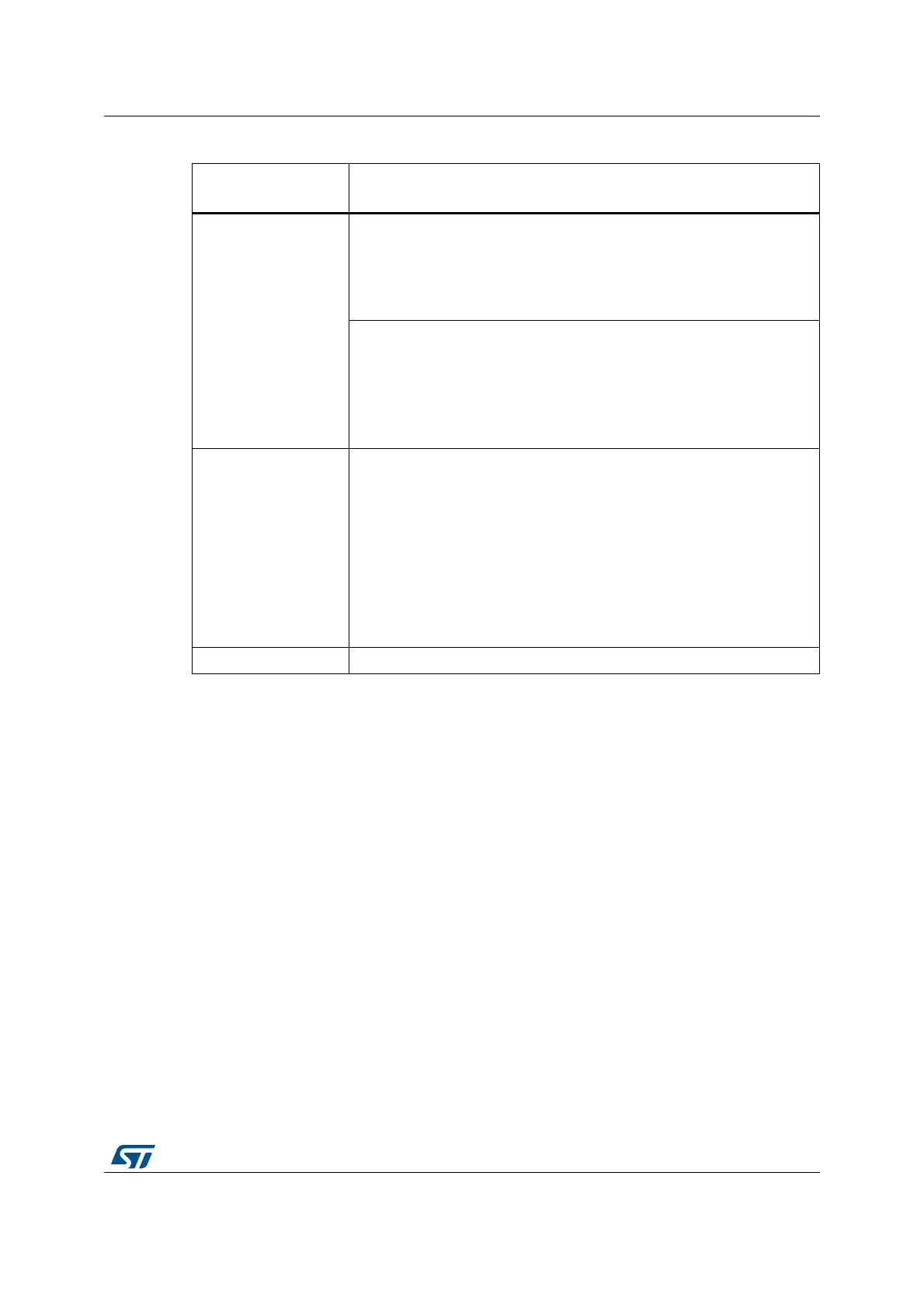

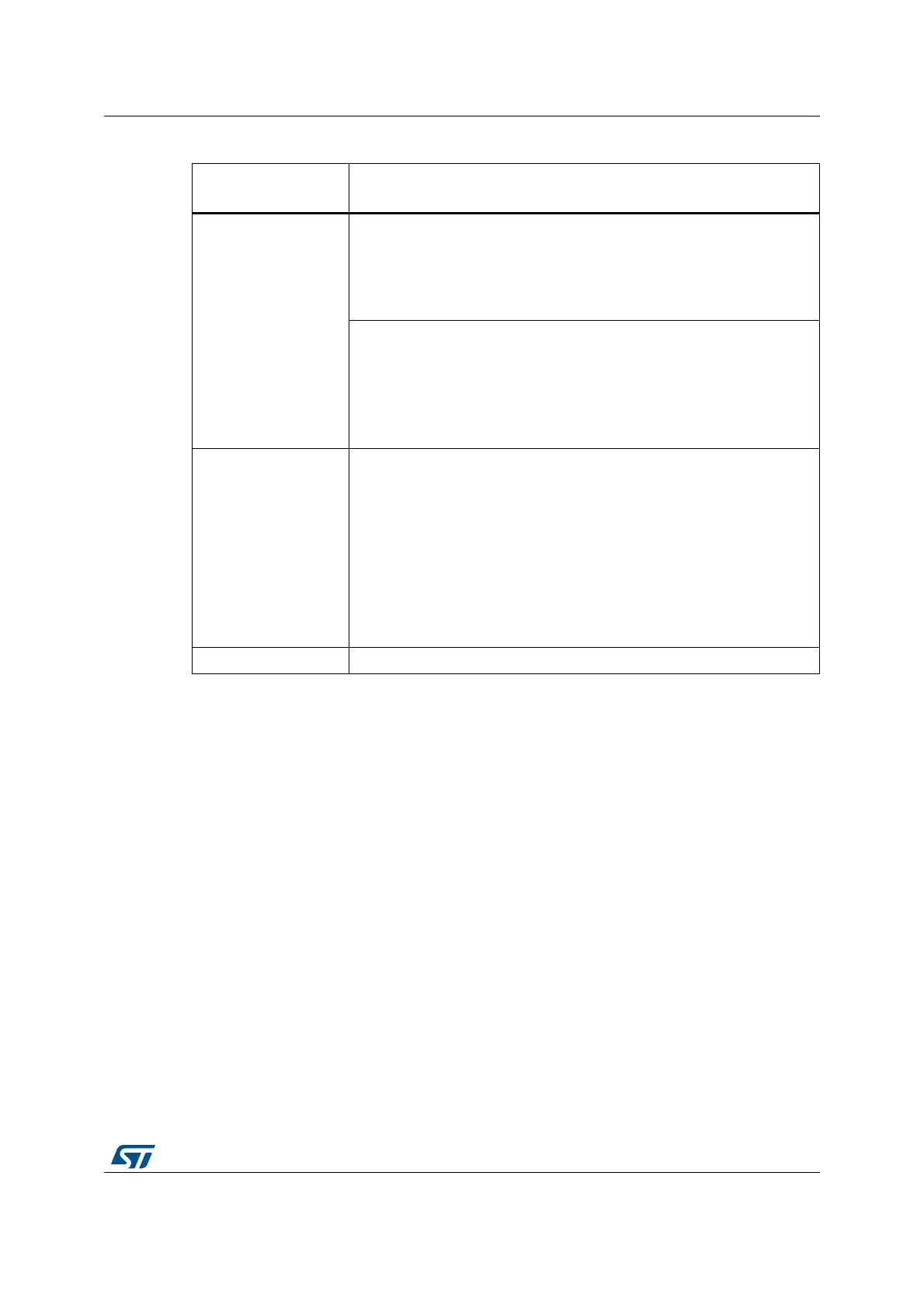

Table 44. Low-power sleep

Low-power sleep-now

mode

Description

Mode entry

Low-power sleep mode is entered from the Low-power run mode.

WFI (Wait for Interrupt) or WFE (Wait for Event) while:

– SLEEPDEEP = 0

– No interrupt (for WFI) or event (for WFE) is pending

Refer to the Cortex

®

-M4 with FPU System Control register.

Low-power sleep mode is entered from the Low-power run mode.

On return from ISR while:

– SLEEPDEEP = 0 and

– SLEEPONEXIT = 1

– No interrupt is pending

Refer to the Cortex

®

-M4 with FPU System Control register.

Mode exit

If WFI or Return from ISR was used for entry

Interrupt: refer to Table 97: STM32G4 Series vector table

If WFE was used for entry and SEVONPEND = 0:

Wakeup event: refer to Section 15.3.2: Wakeup event management

If WFE was used for entry and SEVONPEND = 1:

Interrupt even when disabled in NVIC: refer to Table 97: STM32G4

Series vector table

Wakeup event: refer to Section 15.3.2: Wakeup event management

After exiting the Low-power sleep mode, the MCU is in Low-power run

mode.

Wakeup latency None

Loading...

Loading...