RM0440 Rev 4 1455/2126

RM0440 Basic timers (TIM6/TIM7)

1463

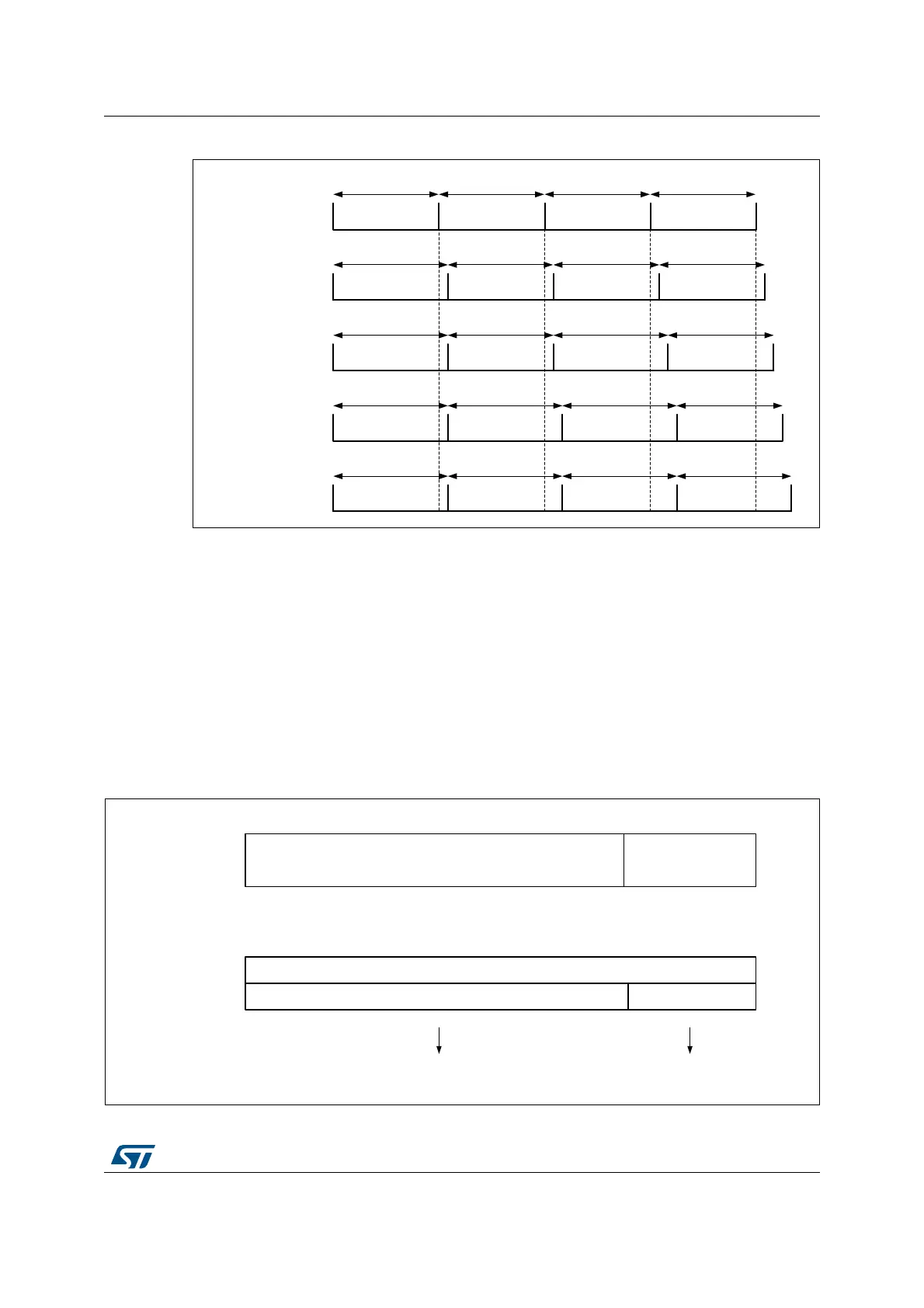

Figure 489. Dithering principle

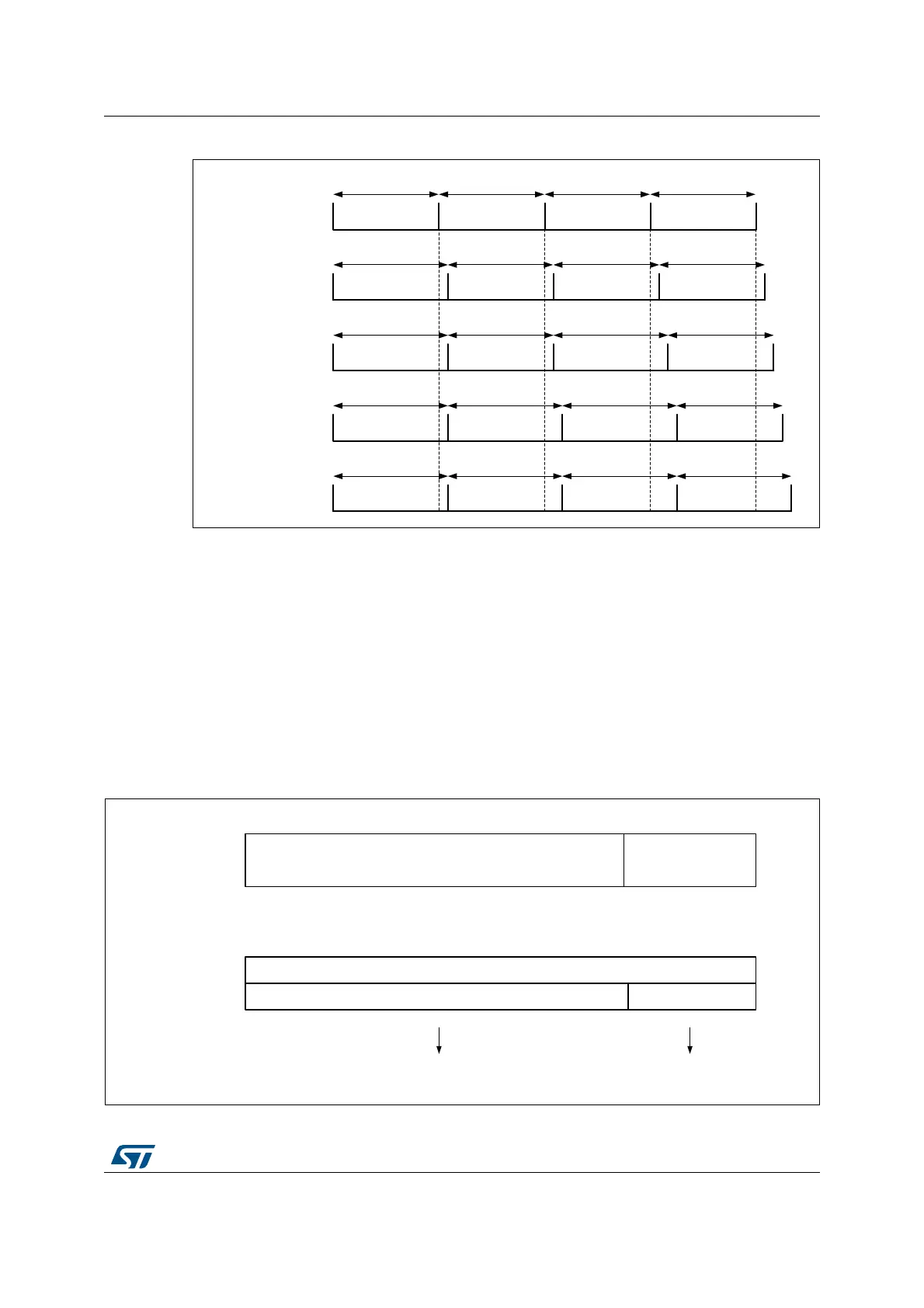

When the dithering mode is enabled, the register coding is changed as following (see

Figure 490 for example):

• the 4 LSBs are coding for the enhanced resolution part (fractional part)

• The MSBs are left-shifted to the bits 19:4 and are coding for the base value

Note: The ARR values will be updated automatically if the DITHEN bit is set / reset (for instance, if

ARR= 0x05 with DITHEN=0, it will be updated to ARR = 0x50 with DITHEN = 1).The

following sequence must be followed when resetting the DITHEN bit:

1. CEN and ARPE bits must be reset

2. The ARR[3:0] bits must be reset

3. The DITHEN bit must be reset

4. The CEN bit can be set ( eventually with ARPE = 1)

Figure 490. Data format and register coding in dithering mode

MSv47466V1

Average period

T = 12

T = 12+¼

T = 12+½

T = 12+¾

T = 13

13

13 13 13

13 13 13 12

13 12 13 12

13 12 12 12

12 12 1212

MSv45753V2

MSB: 16-bits, integer part

LSB: 4-bits

fractional part

326

20 6

Base compare value is 20 during 16 periods

Additional 6 cycles are spread over the

16 periods

Register format in

dithering mode

Example

b0b19

b0b19

Loading...

Loading...