Debug support (DBG) RM0440

2110/2126 RM0440 Rev 4

47.17.9 TPIU registers

The TPIU APB registers can be read and written only if the bit TRCENA of the Debug

Exception and Monitor Control Register (DEMCR) is set. Otherwise, the registers are read

as zero (the output of this bit enables the PCLK of the TPIU).

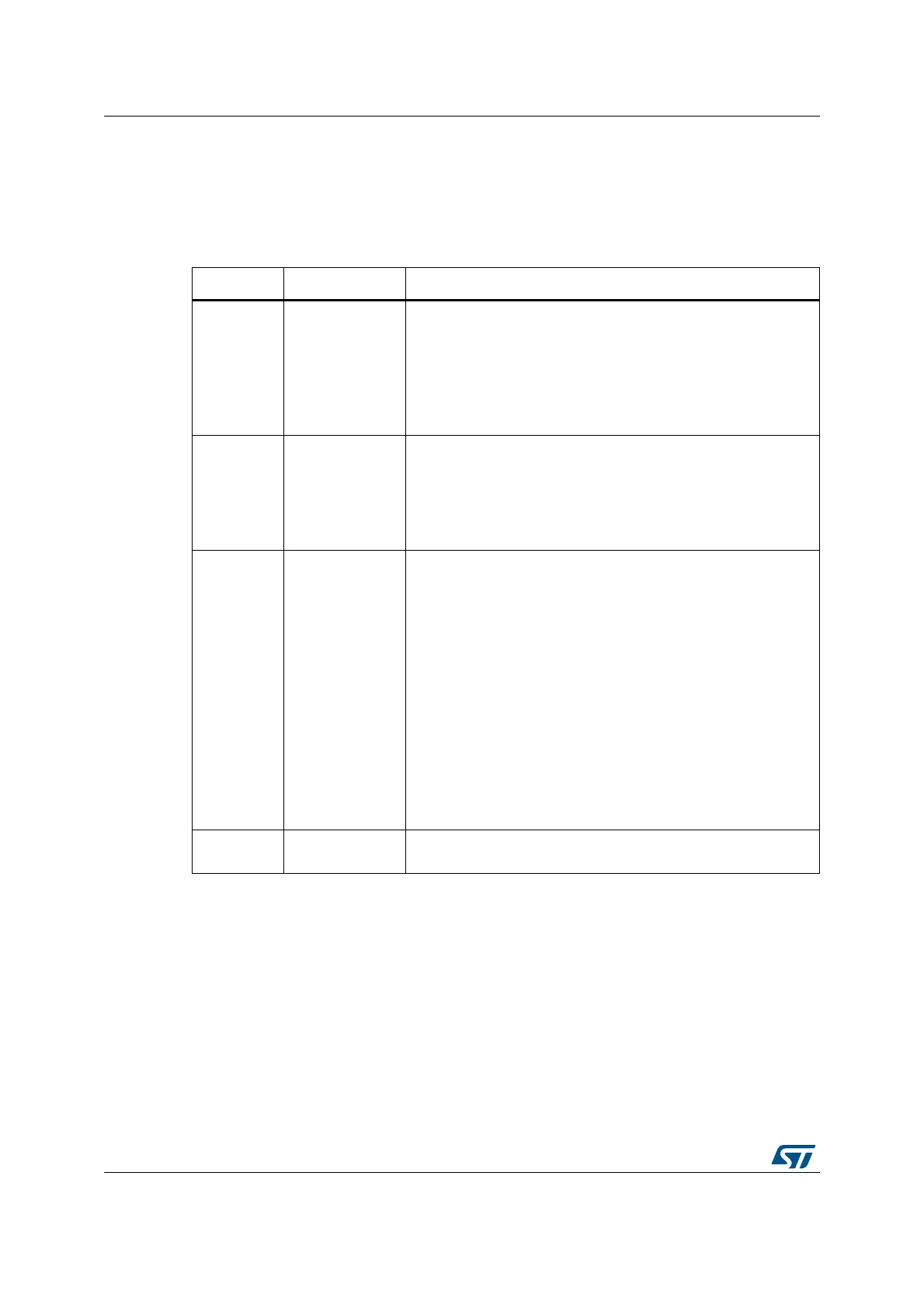

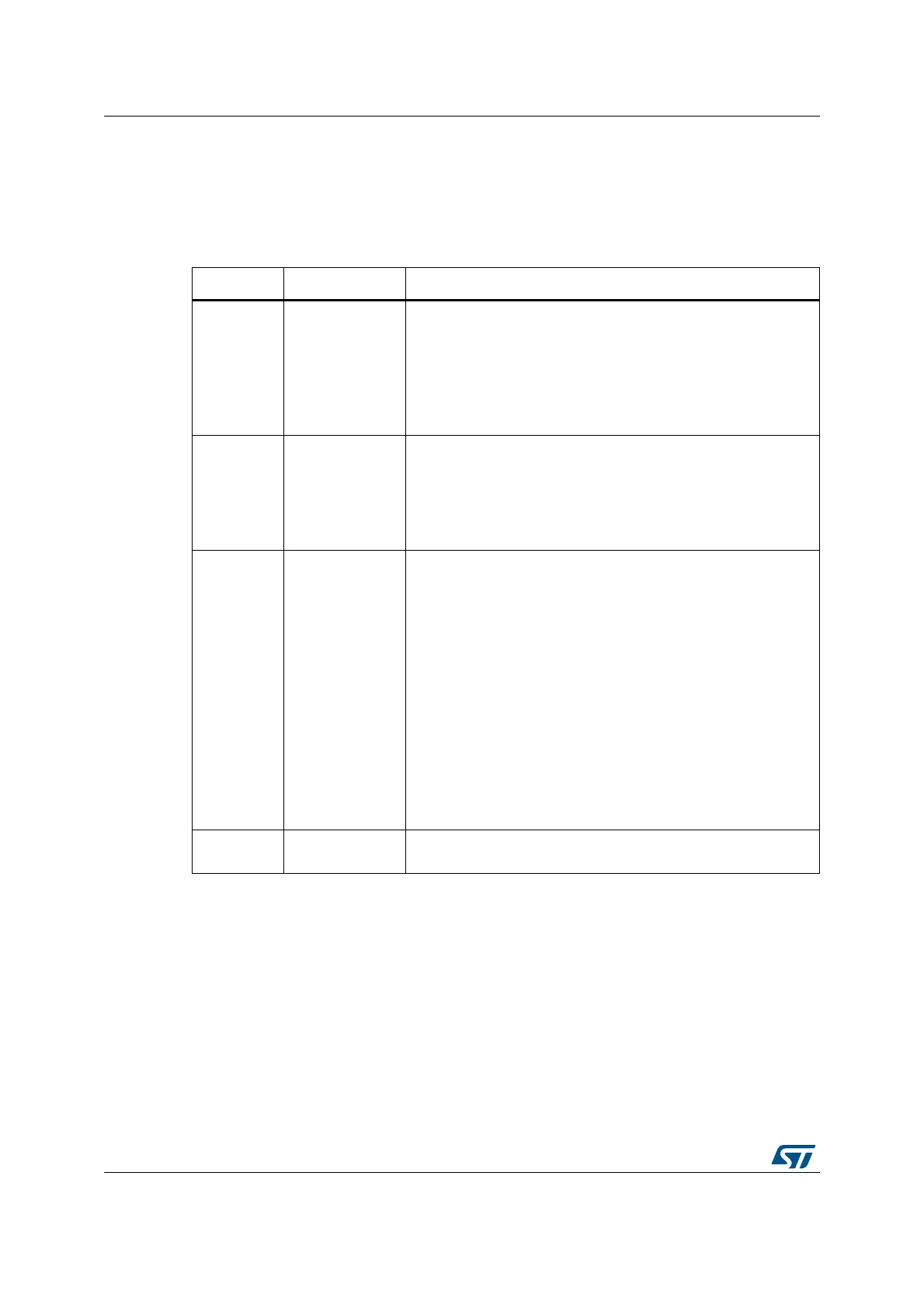

Table 445. Important TPIU registers

Address Register Description

0xE0040004 Current port size

Allows the trace port size to be selected:

Bit 0: Port size = 1

Bit 1: Port size = 2

Bit 2: Port size = 3, not supported

Bit 3: Port Size = 4

Only 1 bit must be set. By default, the port size is one bit.

(0x00000001)

0xE00400F0

Selected pin

protocol

Allows the Trace Port Protocol to be selected:

Bit1:0 =

00: Synchronous Trace Port Mode

01: Serial Wire Output - manchester (default value)

10: Serial Wire Output - NRZ

11: reserved

0xE0040304

Formatter and

flush control

Bit 31-9 = always ‘0’

Bit 8 = TrigIn = always ‘1’ to indicate that triggers are indicated

Bit 7-4 = always 0

Bit 3-2 = always 0

Bit 1 = EnFCont. In Synchronous Trace mode

(Select_Pin_Protocol register bit1:0 = 00), this bit is forced to

‘1’: the formatter is automatically enabled in continuous mode.

In asynchronous mode (Select_Pin_Protocol register bit1:0 <>

00), this bit can be written to activate or not the formatter.

Bit 0 = always ‘0’

The resulting default value is 0x102

Note: In synchronous mode, because the TRACECTL pin is not

mapped outside the chip, the formatter is always enabled in

continuous mode; this way the formatter inserts some control

packets to identify the source of the trace packets).

0xE0040300

Formatter and

flush status

Not used in Cortex

®

-M4 with FPU, always read as 0x00000008

Loading...

Loading...