Serial audio interface (SAI) RM0440

1814/2126 RM0440 Rev 4

Adjusting the delay lines

When the PDM interface is enabled, the application can adjust on-the-fly the delay cells of

each microphone input via SAI_PDMDLY register.

The new delays values will become effective after two TDM frames.

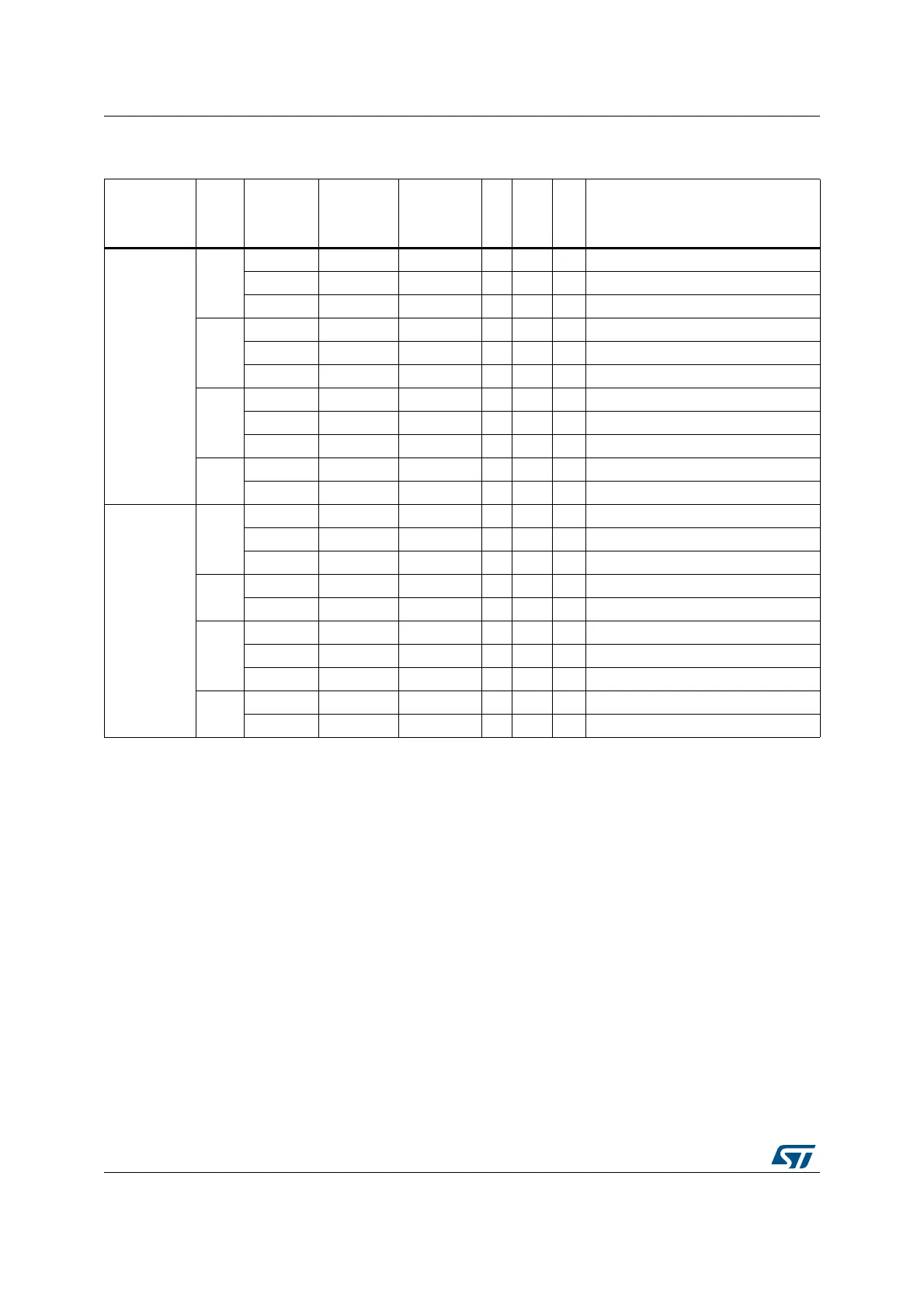

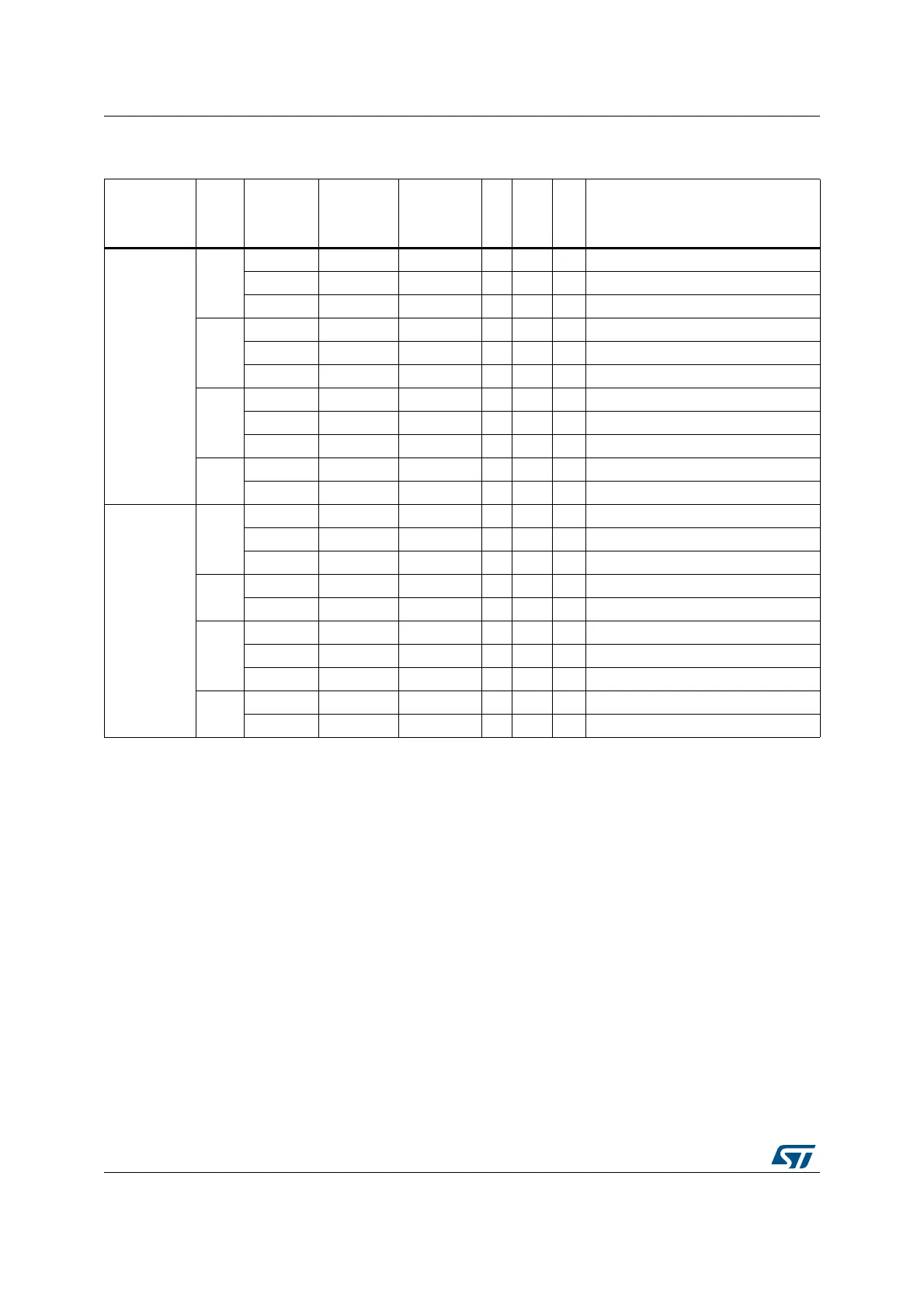

Table 367. Allowed TDM frame configuration

(1)

Microphone

Sample rate

Nber

of Mic

Wanted

SAI_CKn

frequency

bit clock

(SCK_A)

frequency

Frame sync.

(FS_A)

frequency

FRL

DS

NBSLOT

Comments

48 kHz

up to 8

3.072 MHz 24.576 MHz 384 kHz 63 0b111 1 2 slots of 32 bits per frame

3.072 MHz 24.576 MHz 384 kHz 63 0b100 3 4 slots of 16 bits per frame

3.072 MHz 24.576 MHz 384 kHz 63 0b010 7 8 slots of 8 bits per frame

up to 6

3.072 MHz 18.432 MHz 384 kHz 47 0b110 1 2 slots of 24 bits per frame

3.072 MHz 18.432 MHz 384 kHz 47 0b100 2 3 slots of 16 bits per frame

3.072 MHz 18.432 MHz 384 kHz 47 0b010 5 6 slots of 8 bits per frame

up to 4

3.072 MHz 12.288 MHz 384 kHz 31 0b111 0 1 slot of 32 bits per frame

3.072 MHz 12.288 MHz 384 kHz 31 0b100 1 2 slots of 16 bits per frame

3.072 MHz 12.288 MHz 384 kHz 31 0b010 3 4 slots of 8 bits per frame

up to 2

3.072 MHz 6.144 MHz 384 kHz 15 0b100 0 1 slots of 16 bits per frame

3.072 MHz 6.144 MHz 384 kHz 15 0b010 1 2 slots of 8 bits per frame

16 kHz

up to 8

1.024 MHz 8.192 MHz 128 kHz 63 0b111 1 2 slots of 32 bits per frame

1.024 MHz 8.192 MHz 128 kHz 63 0b100 3 4 slots of 16 bits per frame

1.024 MHz 8.192 MHz 128 kHz 63 0b010 7 8 slots of 8 bits per frame

up to 6

1.024 MHz 6.144 MHz 128 kHz 47 0b110 1 2 slots of 24 bits per frame

1.024 MHz 6.144 MHz 128 kHz 47 0b010 5 6 slots of 8 bits per frame

up to 4

1.024 MHz 4.096 MHz 128 kHz 31 0b111 0 1 slot of 32 bits per frame

1.024 MHz 4.096 MHz 128 kHz 31 0b100 1 2 slots of 16 bits per frame

1.024 MHz 4.096 MHz 128 kHz 31 0b010 3 4 slots of 8 bits per frame

up to 2

1.024 MHz 2.048 MHz 128 kHz 15 0b100 0 1 slot of 16 bits per frame

1.024 MHz 2.048 MHz 128 kHz 15 0b010 1 2 slots of 8 bits per frame

1. Refer to Table 366: TDM settings for additional information on TDM configuration. The sai_a_ker_ck clock frequency

provided to the SAI should be a multiple of the SCK_A frequency, and MCKDIV should be programmed accordingly.

2. The table above gives allowed settings for a decimation ratio of 64.

Loading...

Loading...