RM0440 Rev 4 1503/2126

RM0440 AES hardware accelerator (AES)

1538

In CBC decrypt mode, like in ECB decrypt mode, the secret key must be prepared to

perform an AES decryption.

After the key preparation process, the decryption goes as follows: the first 128-bit ciphertext

block (after the swap operation) is used directly as the AES core input block I1 for decrypt

operation, using the 128-bit or 256-bit key. Its output O1 is XOR-ed with the 128-bit IVI field

(that must be identical to that used during encryption) to produce the first plaintext block P1.

The second ciphertext block is processed in the same way as the first block, except that the

I1 data from the first block is used in place of the initialization vector.

The decryption continues in this way until the last complete ciphertext block is decrypted.

If the message size is not a multiple of 128 bits, the final partial data block is decrypted in

the way explained in Section 34.4.6: AES ciphertext stealing and data padding.

For more information on data swapping, refer to Section 34.4.13: AES data registers and

data swapping.

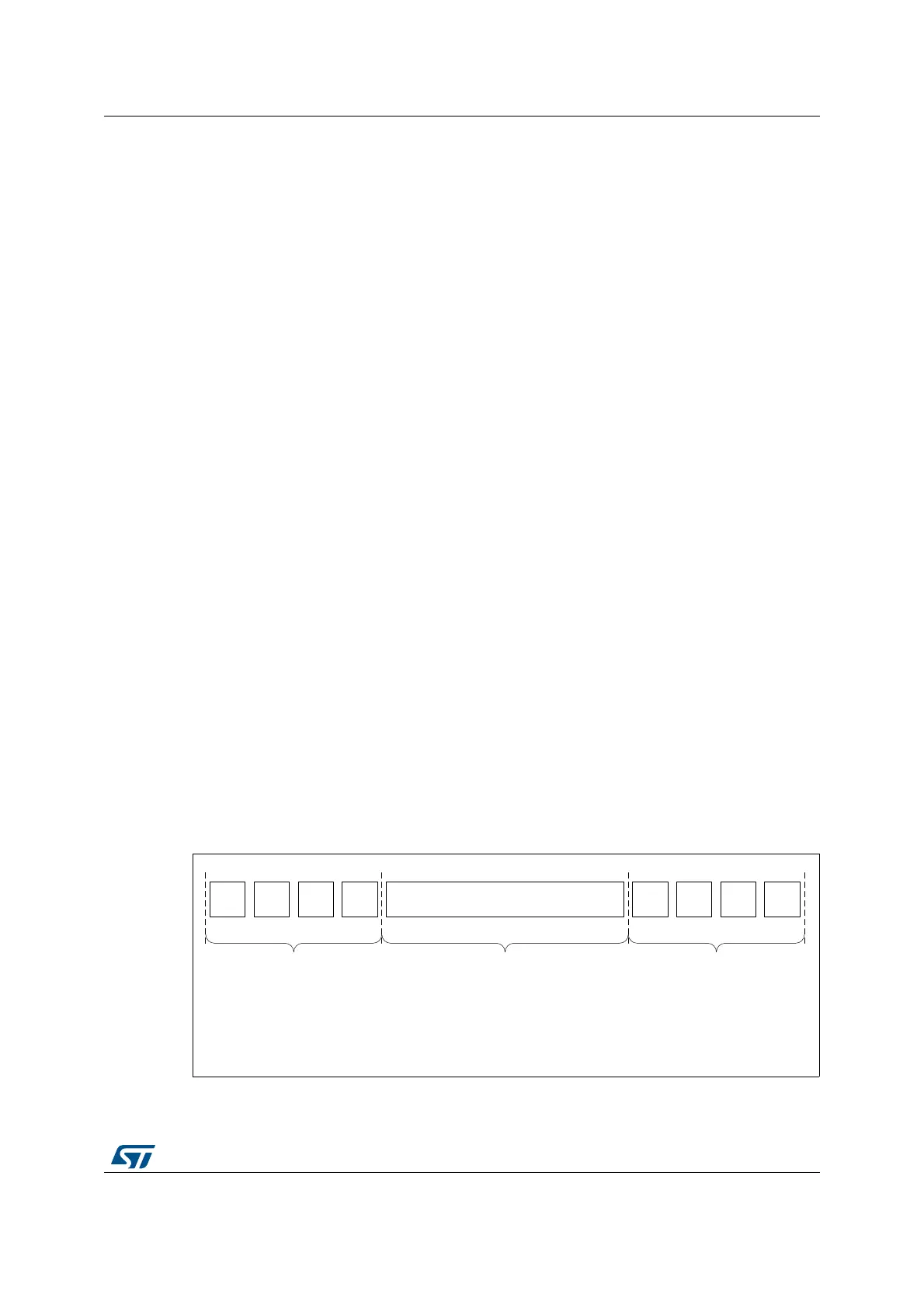

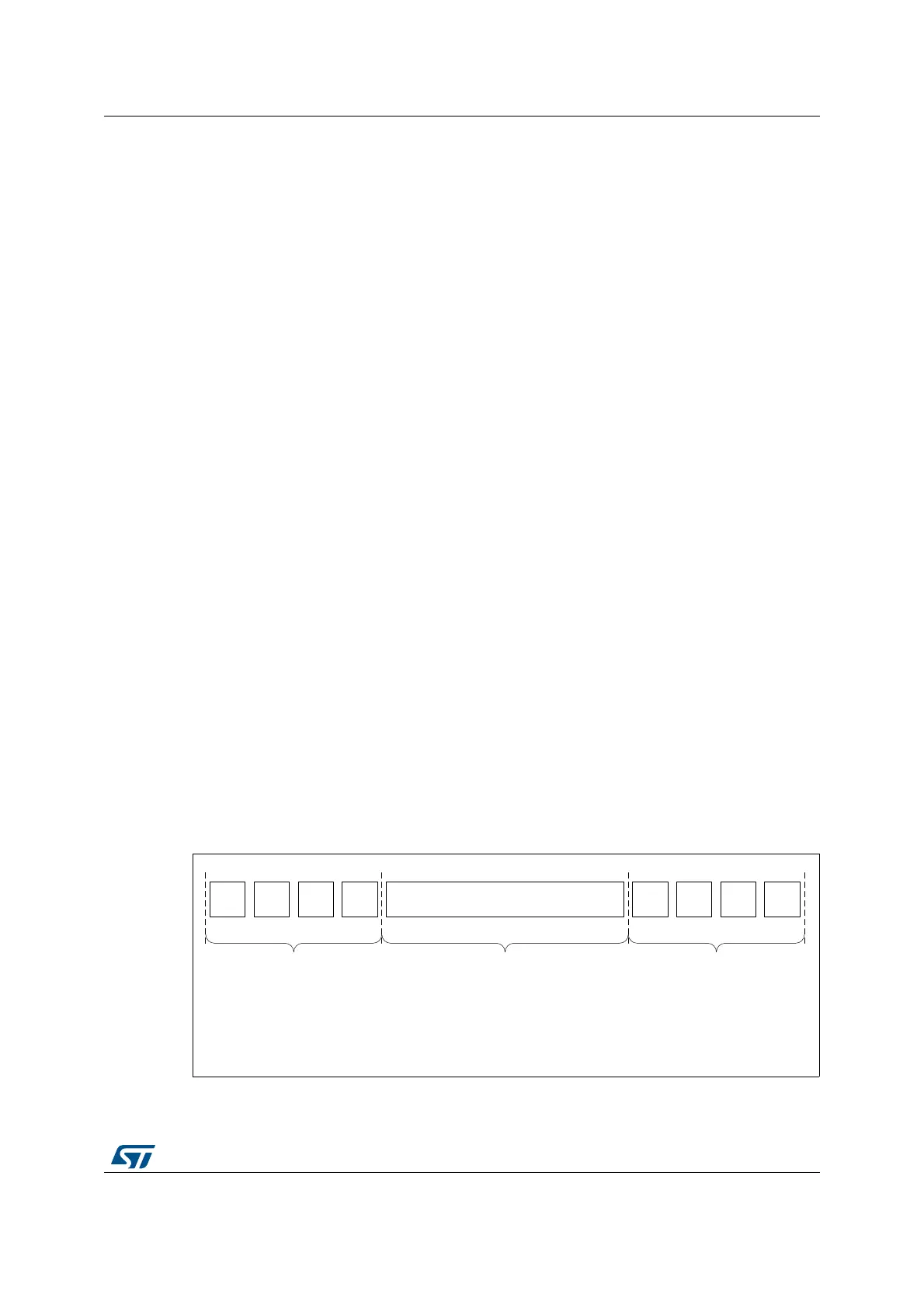

ECB/CBC encryption sequence

The sequence of events to perform an ECB/CBC encryption (more detail in Section 34.4.4):

1. Disable the AES peripheral by clearing the EN bit of the AES_CR register.

2. Select the Mode 1 by setting to 00 the MODE[1:0] bitfield of the AES_CR register and

select ECB or CBC chaining mode by setting the CHMOD[2:0] bitfield of the AES_CR

register to 000 or 001, respectively. Data type can also be defined, using

DATATYPE[1:0] bitfield.

3. Select 128- or 256-bit key length through the KEYSIZE bit of the AES_CR register.

4. Write the AES_KEYRx registers (128 or 256 bits) with encryption key. Fill the

AES_IVRx registers with the initialization vector data if CBC mode has been selected.

5. Enable the AES peripheral by setting the EN bit of the AES_CR register.

6. Write the AES_DINR register four times to input the plaintext (MSB first), as shown in

Figure 514.

7. Wait until the CCF flag is set in the AES_SR register.

8. Read the AES_DOUTR register four times to get the ciphertext (MSB first) as shown in

Figure 514. Then clear the CCF flag by setting the CCFC bit of the AES_CR register.

9. Repeat steps 6-7-8 to process all the blocks with the same encryption key.

Figure 514. ECB/CBC encryption (Mode 1)

MS18936V3

WR

PT3

WR

PT2

WR

PT1

WR

PT0

Wait until flag CCF = 1

RD

CT3

RD

CT2

RD

CT1

RD

CT0

Input phase

4 write operations into

AES_DINR[31:0]

Computation phase

Output phase

4 read operations of

AES_DOUTR[31:0]

PT = plaintext = 4 words (PT3, … , PT0)

CT = ciphertext = 4 words (CT3, … , CT0)

MSB LSB MSB LSB

Loading...

Loading...