RM0440 Rev 4 95/2126

RM0440 Embedded Flash memory (FLASH) for category 3 devices

228

3.3.2 Error code correction (ECC)

Dual bank mode (DBANK=1, 64-bits data width)

Data in Flash memory are 72-bits words: 8 bits are added per double word (64 bits). The

ECC mechanism supports:

• One error detection and correction

• Two errors detection

When one error is detected and corrected, the flag ECCC (ECC correction) is set in Flash

ECC register (FLASH_ECCR). If ECCCIE is set, an interrupt is generated.

When two errors are detected, a flag ECCD (ECC detection) is set in FLASH_ECCR

register. In this case, a NMI is generated.

When an ECC error is detected, the address of the failing double word and its associated

bank are saved in ADDR_ECC[20:0] and BK_ECC in the FLASH_ECCR register.

ADDR_ECC[2:0] are always cleared.

When ECCC or ECCD is set, ADDR_ECC and BK_ECC are not updated if a new ECC error

occurs. FLASH_ECCR is updated only when ECC flags are cleared.

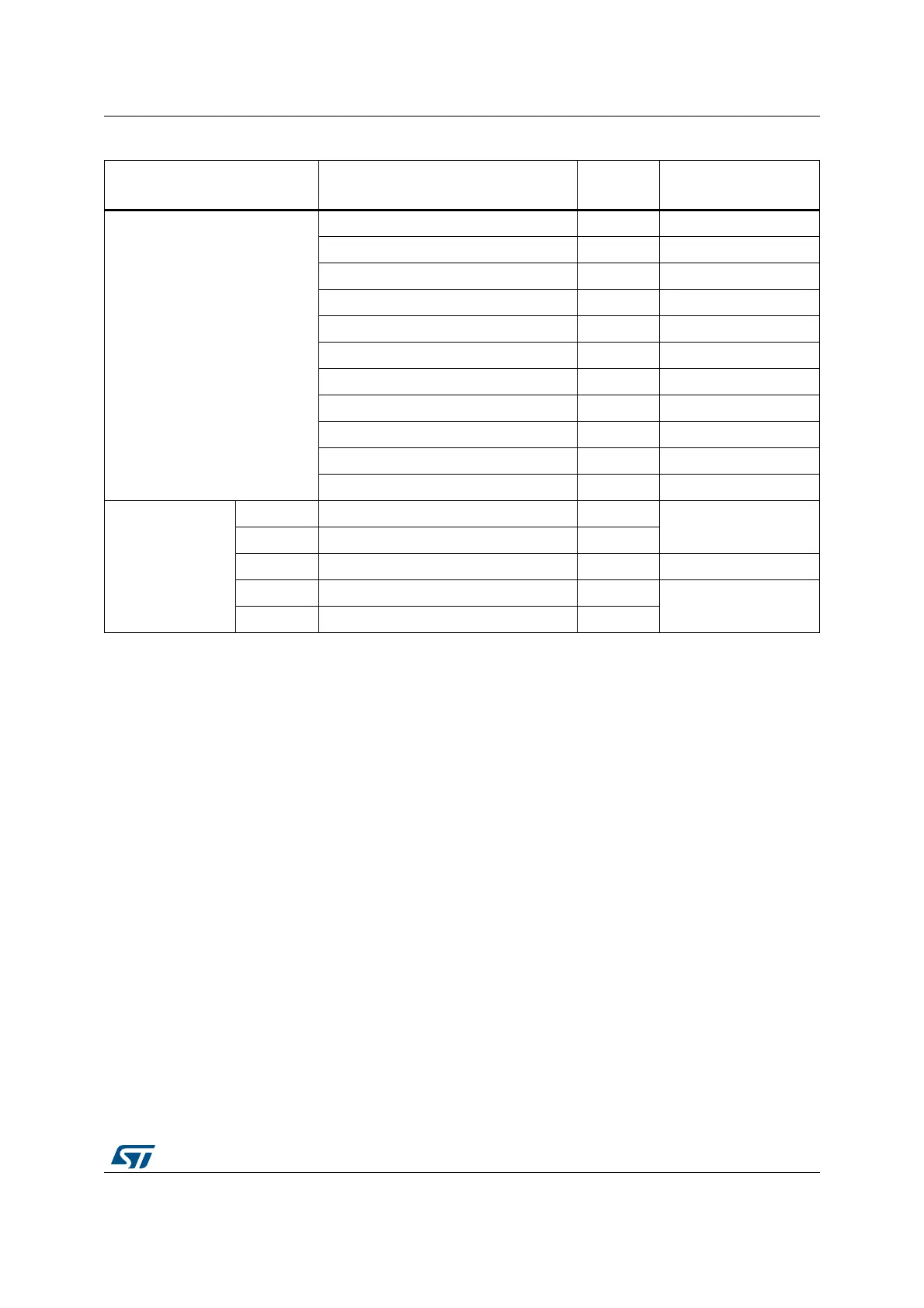

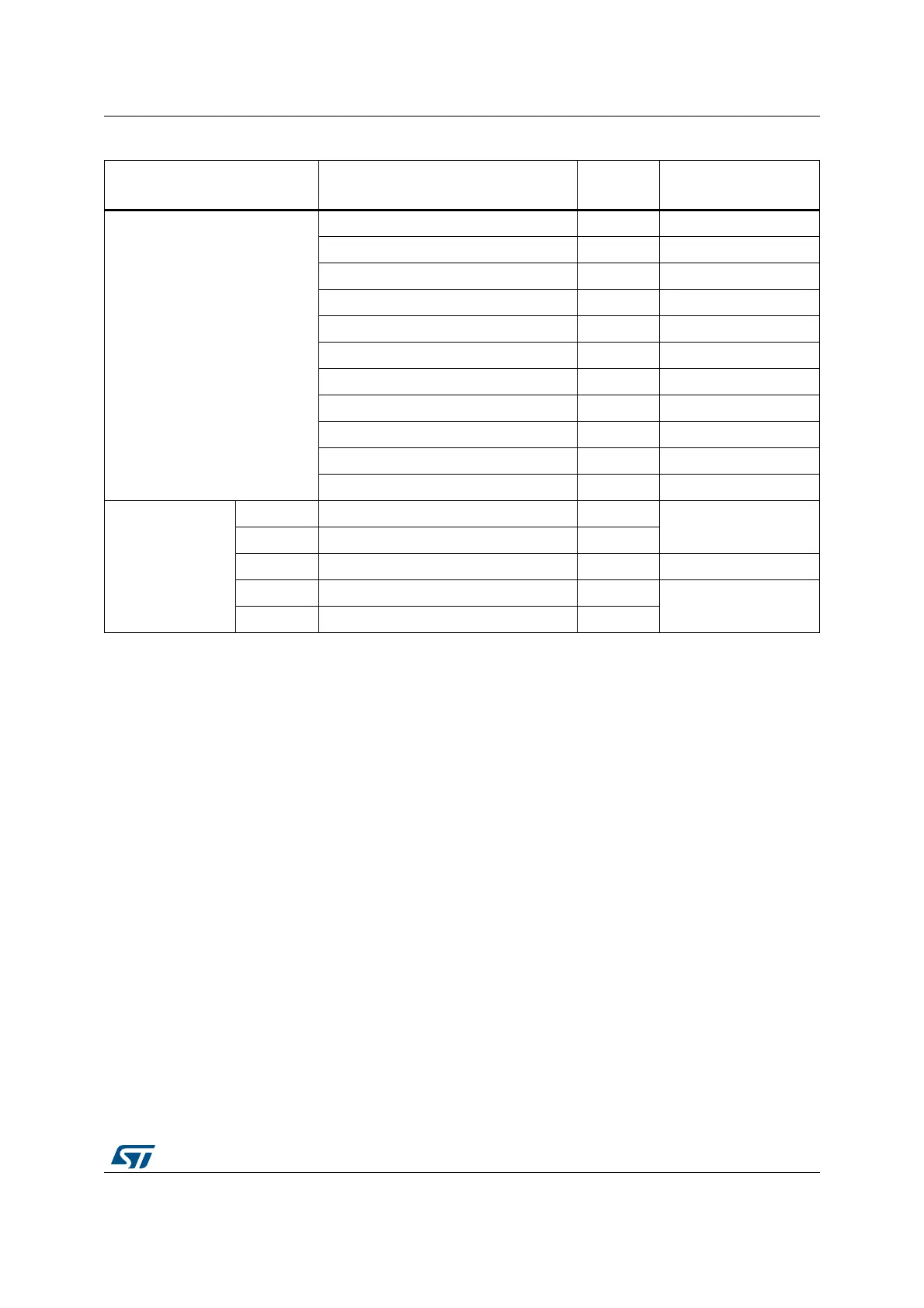

Table 8. Flash module - 512/256/128 KB single bank organization (128 bits read width)

Flash area Flash memory addresses

Size

(bytes)

Name

Main memory

(512/256/128 KB)

0x0800 0000 - 0x0800 0FFF 4 K Page 0

0x0800 1000 - 0x0800 1FFF 4 K Page 1

0x0800 2000 - 0x0800 2FFF 4 K Page 2

---

---

---

---

---

---

---

0x0807 F000 - 0x0807 FFFF 4 K Page 127

Information block

Bank 1 0x1FFF 0000 - 0x1FFF 6FFF 28 K

System memory

Bank 2 0x1FFF 8000 - 0x1FFF EFFF 28 K

Bank 1 0x1FFF 7000 - 0x1FFF 73FF 1 K OTP area

Bank 1 0x1FFF 7800 - 0x1FFF 782F 48

Option bytes

Bank 2 0x1FFF F800 - 0x1FFF F82F 48

Loading...

Loading...