RM0440 Rev 4 1527/2126

RM0440 AES hardware accelerator (AES)

1538

34.7 AES registers

34.7.1 AES control register (AES_CR)

Address offset: 0x00

Reset value: 0x0000 0000

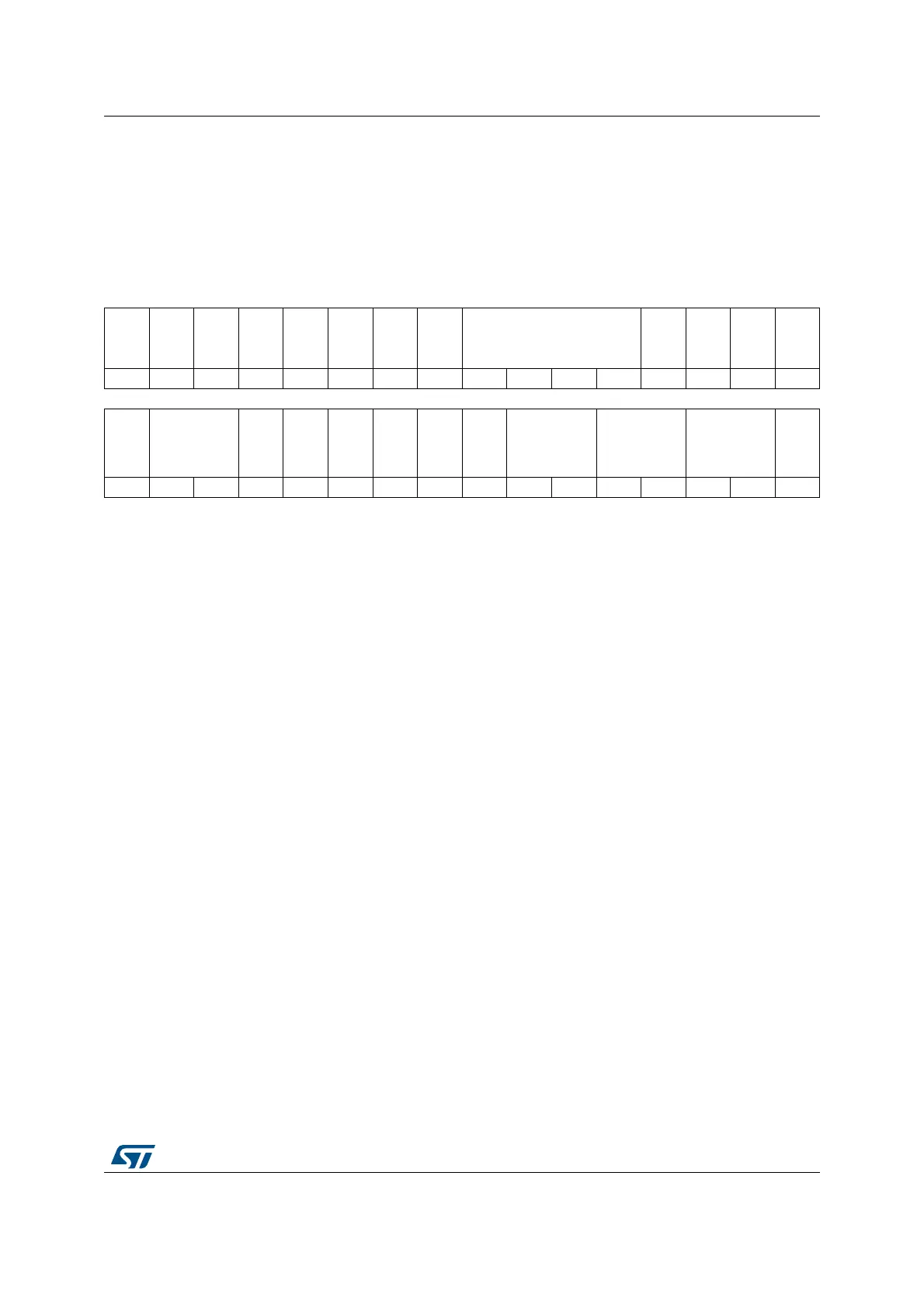

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. NPBLB[3:0] Res.

KEYSIZE

Res.

CHMOD[2]

rw rw rw rw rw rw

1514131211109876543210

Res. GCMPH[1:0]

DMAOUTEN

DMAINEN

ERRIE CCFIE ERRC CCFC CHMOD[1:0] MODE[1:0] DATATYPE[1:0] EN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:20 NPBLB[3:0]: Number of padding bytes in last block

The bitfield sets the number of padding bytes in last block of payload:

0000: All bytes are valid (no padding)

0001: Padding for one least-significant byte of last block

...

1111: Padding for 15 least-significant bytes of last block

Bit 19 Reserved, must be kept at reset value.

Bit 18 KEYSIZE: Key size selection

This bitfield defines the length of the key used in the AES cryptographic core, in bits:

0: 128

1: 256

Attempts to write the bit are ignored when the EN bit of the AES_CR register is set before the write

access and it is not cleared by that write access.

Bit 17 Reserved, must be kept at reset value.

Bit 16 CHMOD[2]: Chaining mode selection, bit [2]

Refer to the bits [5:6] of the register for the description of the CHMOD[2:0] bitfield

Bit 15 Reserved, must be kept at reset value.

Bits 14:13 GCMPH[1:0]: GCM or CCM phase selection

This bitfield selects the phase of GCM, GMAC or CCM algorithm:

00: Init phase

01: Header phase

10: Payload phase

11: Final phase

The bitfield has no effect if other than GCM, GMAC or CCM algorithms are selected (through the

ALGOMODE bitfield).

Loading...

Loading...