RM0440 Rev 4 1959/2126

RM0440 FD controller area network (FDCAN)

2008

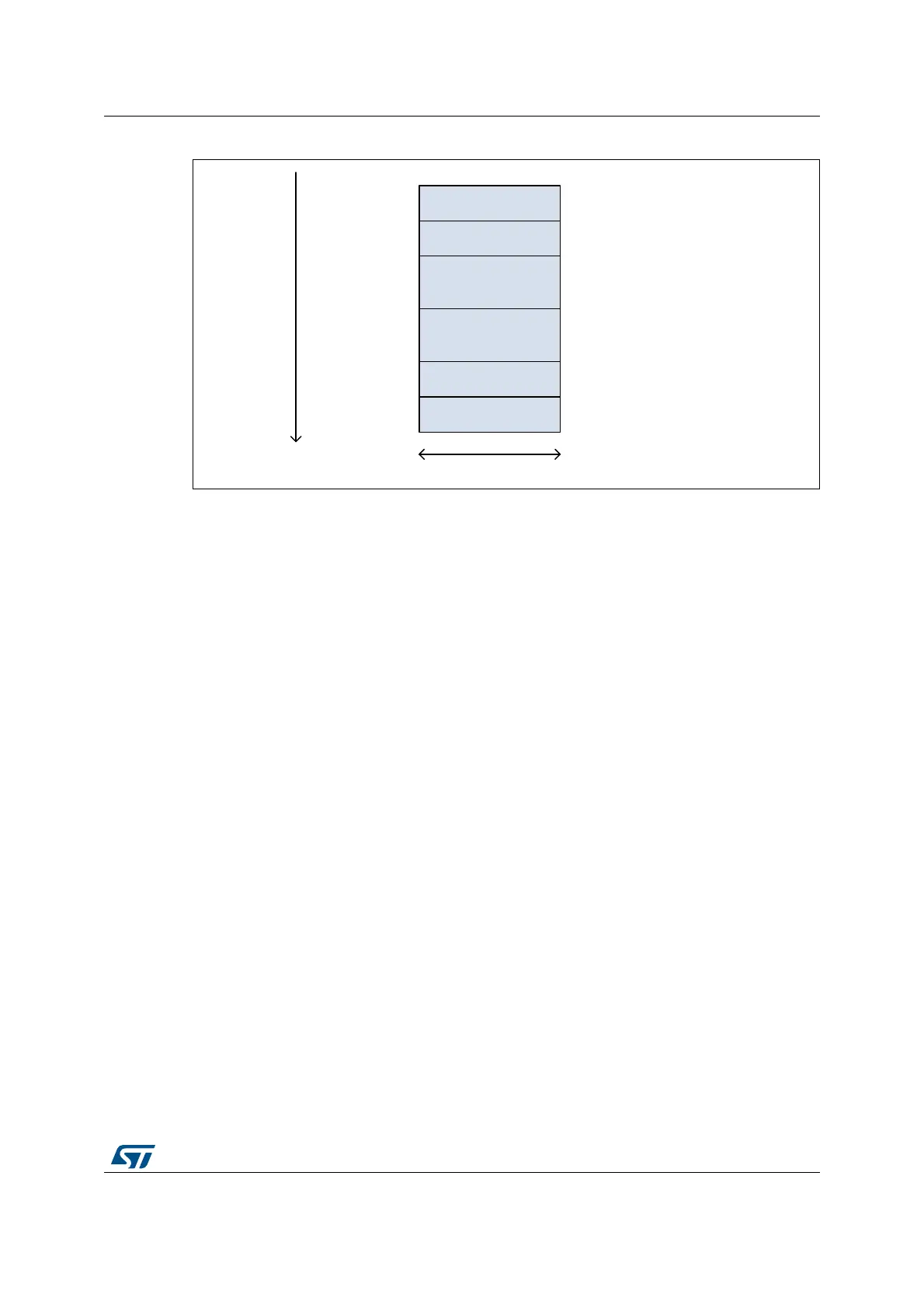

Figure 668. Message RAM configuration

When the FDCAN addresses the Message RAM, it addresses 32-bit words (aligned), not a

single byte. The RAM address are 32-bit words, i.e. only bits 15 to 2 are evaluated, the two

least significant bits are ignored.

Rx handling

The Rx Handler controls the acceptance filtering, the transfer of received messages to Rx to

one of the two Rx FIFOs, as well as the Rx FIFO Put and Get Indexes.

Acceptance filter

The FDCAN offers the possibility to configure two sets of acceptance filters, one for

standard identifiers and another for extended identifiers. These filters can be assigned to Rx

FIFO 0 or Rx FIFO 1. For acceptance filtering each list of filters is executed from element #0

until the first matching element. Acceptance filtering stops at the first matching element.

Following filter elements are not evaluated for this message.

The main features are:

• Each filter element can be configured as

– range filter (from - to)

– filter for one or two dedicated IDs

– classic bit mask filter

• Each filter element is configurable for acceptance or rejection filtering

• Each filter element can be enabled/disabled individually

• Filters are checked sequentially, execution stops with the first matching filter element

Related configuration registers are:

• Global Filter Configuration (RXGFC)

• Extended ID AND Mask (XIDAM)

MS47278V3

32 bits

Tx buffers

Tx event FIFO

Rx FIFO 1

Rx FIFO 0

29-bit filter

11-bit filter

TBSA = 0x0278

EFSA = 0x0260

F1SA = 0x188

F0SA = 0x00B0

FLESA = 0x0070

FLSSA = 0x0000

3 elements / 54 words

3 elements / 6 words

3 elements / 54 words

3 elements / 54 words

8 elements / 16 words

28 elements / 28 words

0x0350

Loading...

Loading...