RM0440 Rev 4 1989/2126

RM0440 FD controller area network (FDCAN)

2008

44.4.16 FDCAN interrupt enable register (FDCAN_IE)

The settings in the interrupt enable register determine which status changes in the interrupt

register are signaled on an interrupt line.

Address offset: 0x0054

Reset value: 0x0000 0000

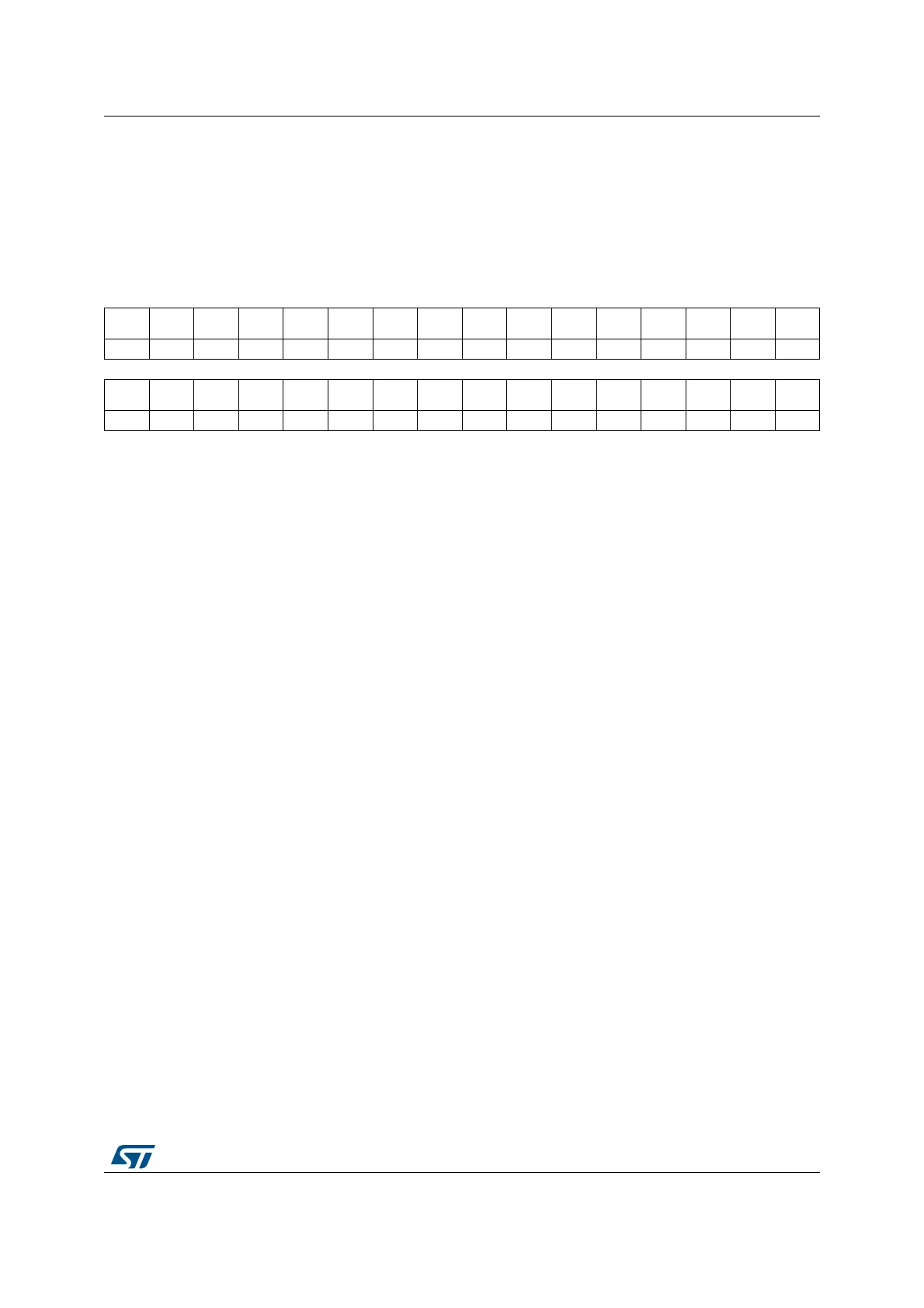

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. ARAE PEDE PEAE WDIE BOE EWE EPE ELOE

rw rw rw rw rw rw rw rw

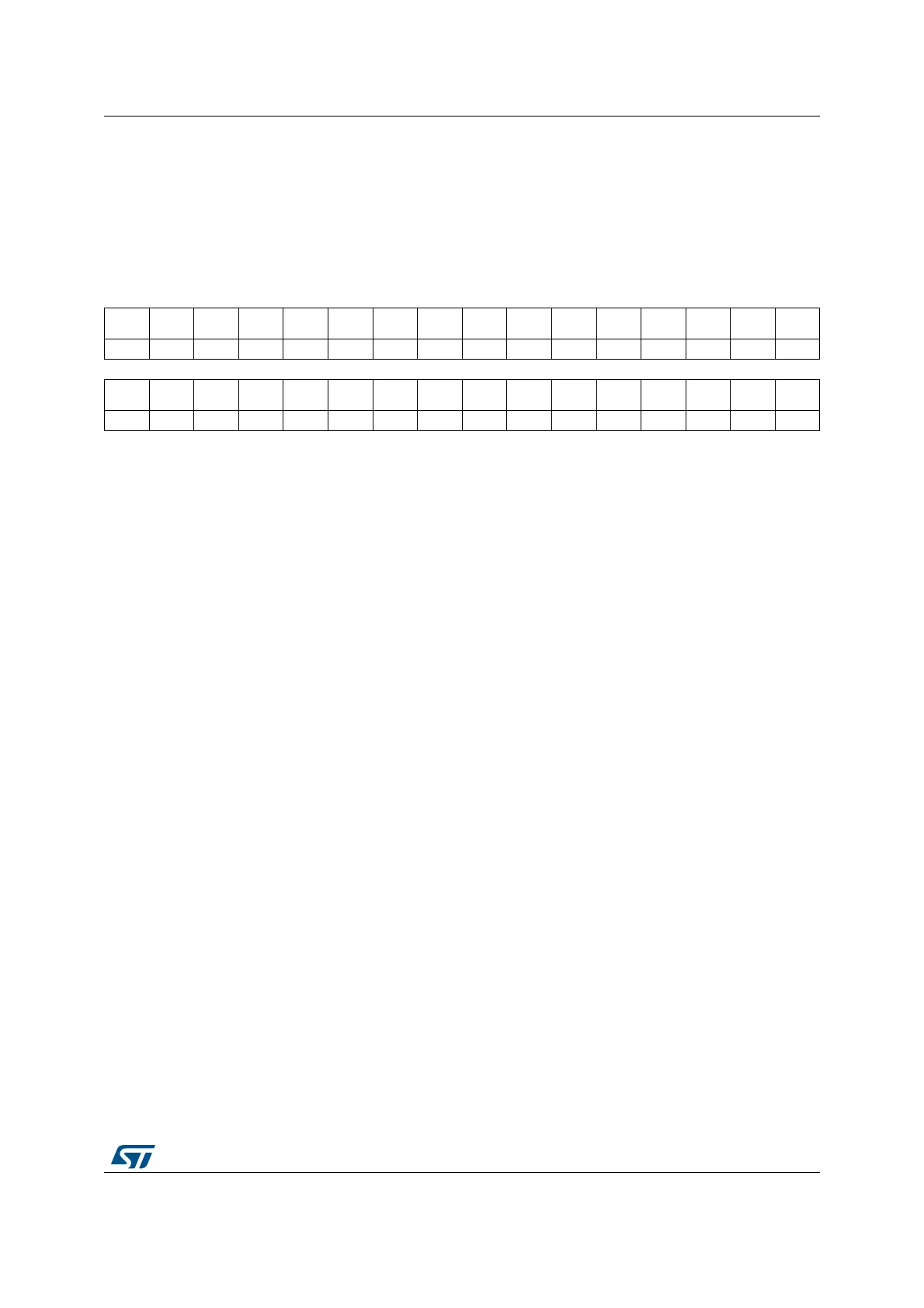

1514131211109876543210

TOOE MRAFE TSWE TEFLE TEFFE TEFNE TFEE TCFE TCE HPME RF1LE RF1FE RF1NE RF0LE RF0FE RF0NE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 ARAE: Access to reserved address enable

Bit 22 PEDE: Protocol error in data phase enable

Bit 21 PEAE: Protocol error in arbitration phase enable

Bit 20 WDIE: Watchdog interrupt enable

0: Interrupt disabled

1: Interrupt enabled

Bit 19 BOE: Bus_Off status

0: Interrupt disabled

1: Interrupt enabled

Bit 18 EWE: Warning status interrupt enable

0: Interrupt disabled

1: Interrupt enabled

Bit 17 EPE: Error passive interrupt enable

0: Interrupt disabled

1: Interrupt enabled

Bit 16 ELOE: Error logging overflow interrupt enable

0: Interrupt disabled

1: Interrupt enabled

Bit 15 TOOE: Timeout occurred interrupt enable

0: Interrupt disabled

1: Interrupt enabled

Bit 14 MRAFE: Message RAM access failure interrupt enable

0: Interrupt disabled

1: Interrupt enabled

Bit 13 TSWE: Timestamp wraparound interrupt enable

0: Interrupt disabled

1: Interrupt enabled

Loading...

Loading...