USB Type-C™ / USB Power Delivery interface (UCPD) RM0440

2054/2126 RM0440 Rev 4

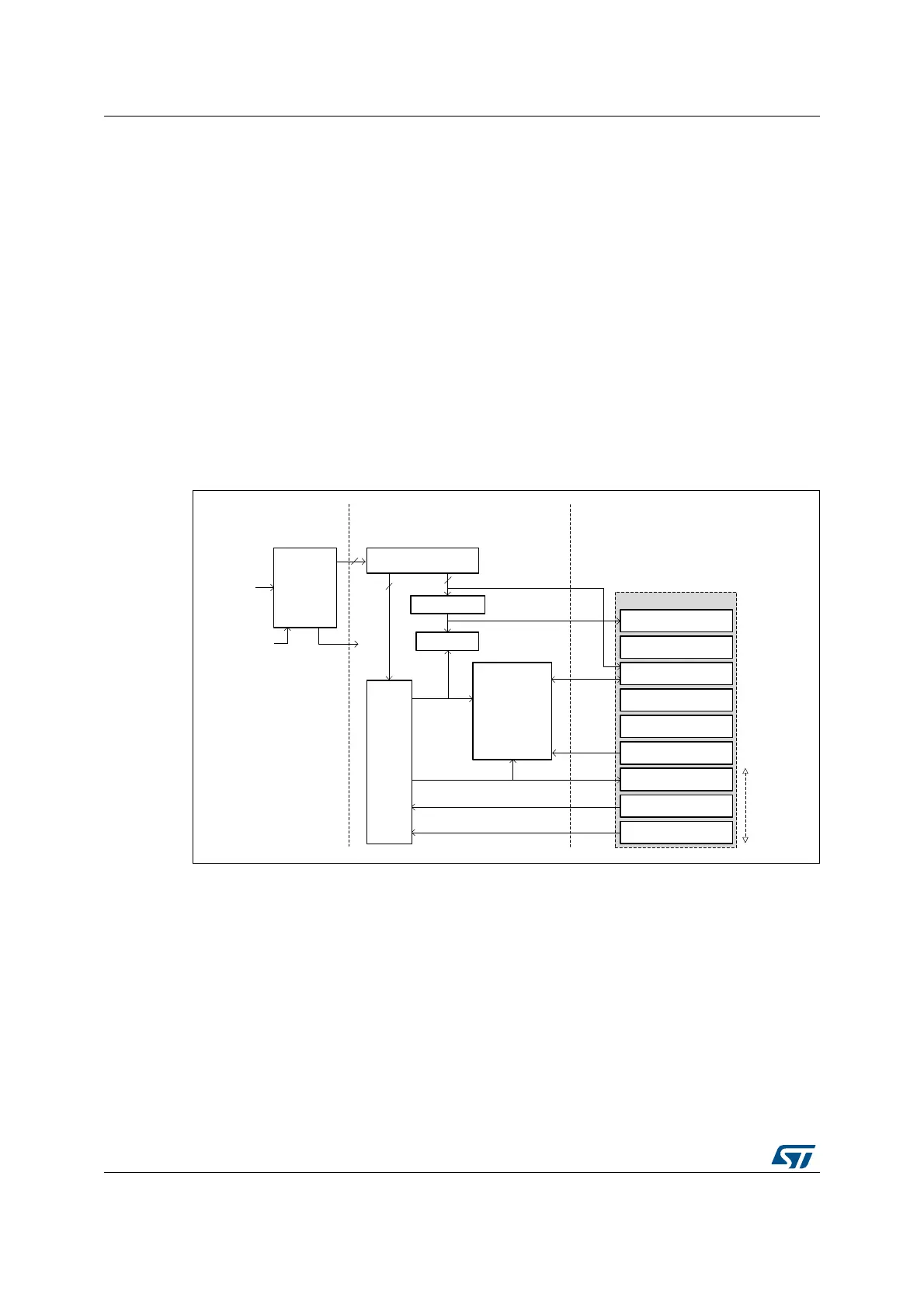

46.4.5 UCPD BMC receiver

The UCPD BMC receiver performs:

• Clock recovery

• Preamble detection / timing derivation

• BMC decoding

• 4b5b decoding

• K-code ordered set recognition

• CRC checking

• SOP detection

• EOP detection

The receiver is activated as soon as the UCPD peripheral is enabled (via UCPDEN), but it

waits for an idle CC line state before attempting to receive a message.

The following figure shows the UCPD BMC receiver high-level architecture.

Figure 683. UCPD BMC receiver architecture

CRC checker

The received bits are fed into a CRC checker which evolves a 32-bit state during the

received the payload bitstream. At the end the 32 bits of the CRC also fed into the logic

The EOP detection (5 bits) halts the process and a check is performed for the fixed residual

state which confirms correct reception of the payload (in fact the residual is 0xC704DD78).

At this point the UCPD raises interrupt

RXMSGEND. If the CRC was not correct then RXERR

is set true and the receive data must be discarded.

Under normal operation, this interrupt would previously have been acknowledged and thus

cleared. If this is not the case, a different interrupt

RXOVR is generated in place of

RXMSGEND.

MSv45545V2

CRC check

USB PD

receiver

state machine

Clock

recovery /

BMC

decode

UCPD_RX_ORDSET

ucpd_pclk

clock domain

From

analog PHY

ucpd_rx_clk

clock domain

ucpd_clk

clock domain

Ordered

set type

Registers

UCPD_CR

UCPD_IMR

UCPD_ICR

UCPD_SR

UCPD_RX_PAYSZ

UCPD_RXDR

UCPD_RX_ORDSET1

UCPD_RX_ORDSET2

Ordered

set /

EOP

detect

EOP found

4b5b decode

20-bit FIFO

20

5 latest

Manage

status flags

Message

type

Ordered set

detect/type

For future

extensions

ucpd_clk

1

ucpd_rx_clk

Interrupt clear

Interrupt mask

Rx control

Rx status flags

Rx payload size

Rx payload data

Loading...

Loading...