Reset and clock control (RCC) RM0440

290/2126 RM0440 Rev 4

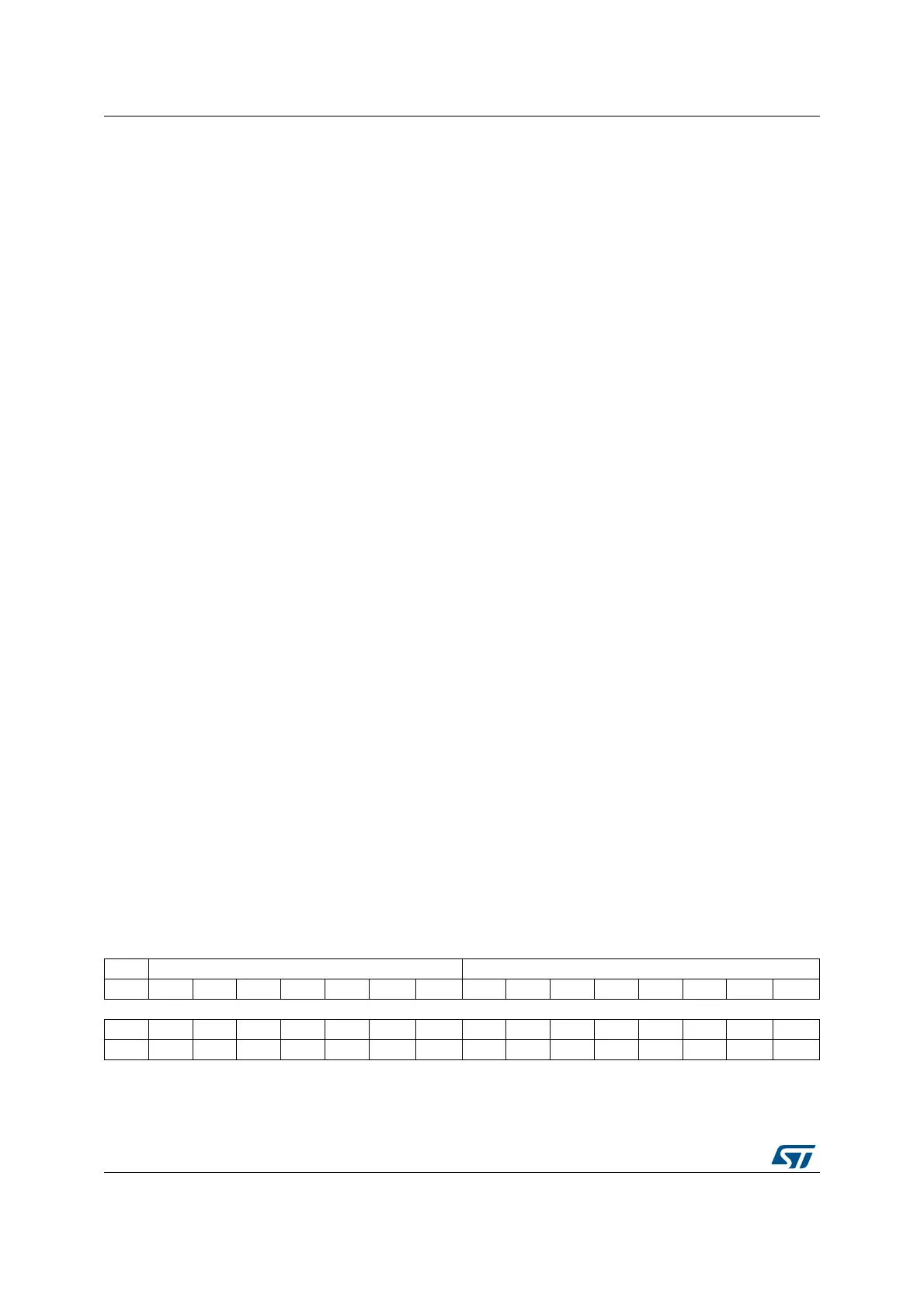

7.4.2 Internal clock sources calibration register (RCC_ICSCR)

Address offset: 0x04

Reset value: 0x40XX 00XX

where X is factory-programmed.

Access: no wait state, word, half-word and byte access

Bit 16 HSEON: HSE clock enable

Set and cleared by software.

Cleared by hardware to stop the HSE oscillator when entering Stop, Standby or Shutdown

mode. This bit cannot be reset if the HSE oscillator is used directly or indirectly as the system

clock.

0: HSE oscillator OFF

1: HSE oscillator ON

Bits 15:11 Reserved, must be kept at reset value.

Bit 10 HSIRDY: HSI16 clock ready flag

Set by hardware to indicate that HSI16 oscillator is stable. This bit is set only when HSI16 is

enabled by software by setting HSION.

0: HSI16 oscillator not ready

1: HSI16 oscillator ready

Note: Once the HSION bit is cleared, HSIRDY goes low after 6 HSI16 clock cycles.

Bit 9 HSIKERON: HSI16 always enable for peripheral kernels.

Set and cleared by software to force HSI16 ON even in Stop modes. The HSI16 can only

feed USARTs and I

2

Cs peripherals configured with HSI16 as kernel clock. Keeping the

HSI16 ON in Stop mode allows to avoid slowing down the communication speed because of

the HSI16 startup time. This bit has no effect on HSION value.

0: No effect on HSI16 oscillator.

1: HSI16 oscillator is forced ON even in Stop mode.

Bit 8 HSION: HSI16 clock enable

Set and cleared by software.

Cleared by hardware to stop the HSI16 oscillator when entering Stop, Standby or Shutdown

mode.

Set by hardware to force the HSI16 oscillator ON when STOPWUCK=1 or HSIASFS = 1

when leaving Stop modes, or in case of failure of the HSE crystal oscillator.

This bit is set by hardware if the HSI16 is used directly or indirectly as system clock.

0: HSI16 oscillator OFF

1: HSI16 oscillator ON

Bits 7:0 Reserved, must be kept at reset value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. HSITRIM[6:0] HSICAL[7:0]

rwrwrwrwrwrwrwrrrrrr r r

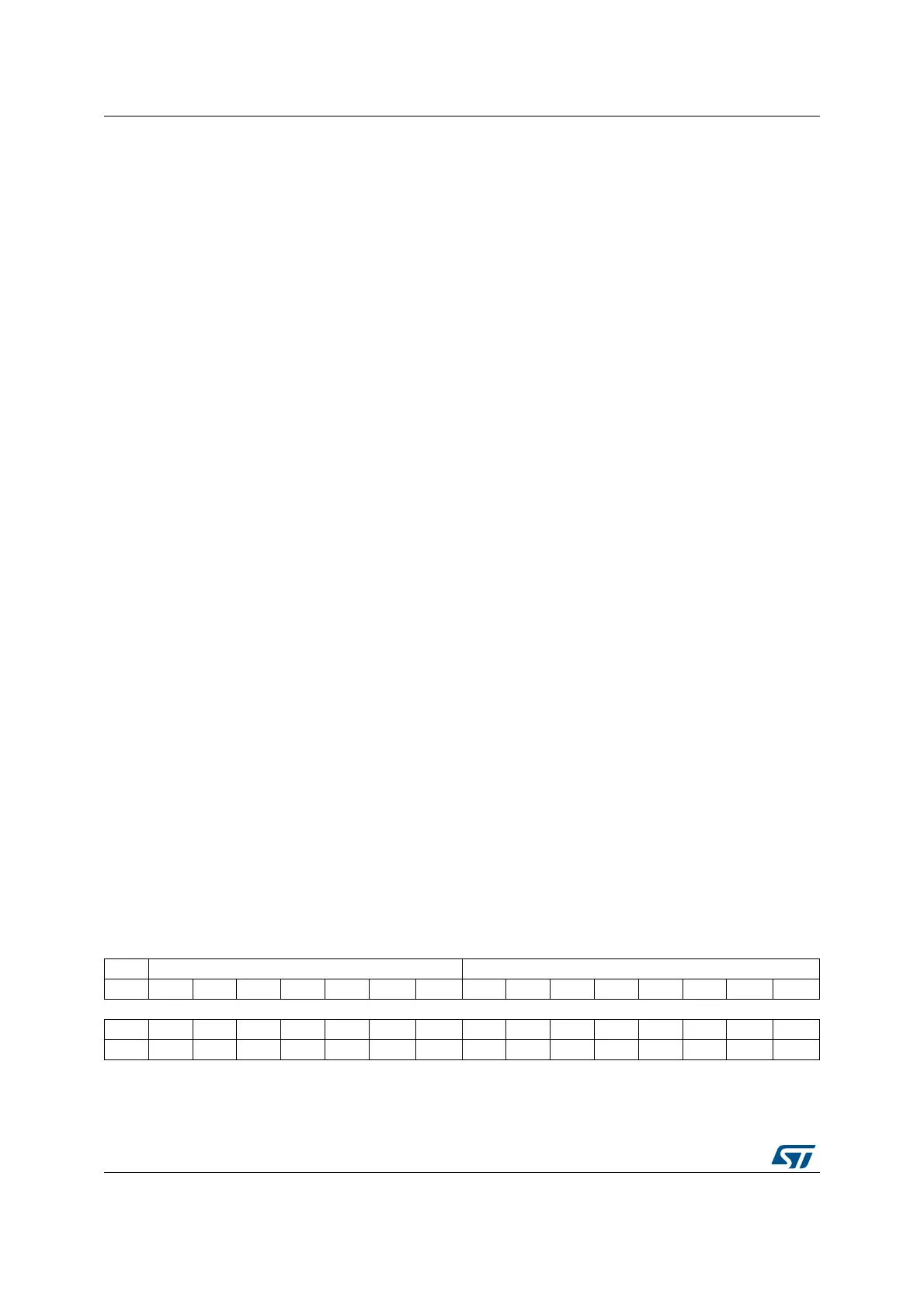

1514131211109 8 765432 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

Loading...

Loading...