Clock recovery system (CRS) RM0440

348/2126 RM0440 Rev 4

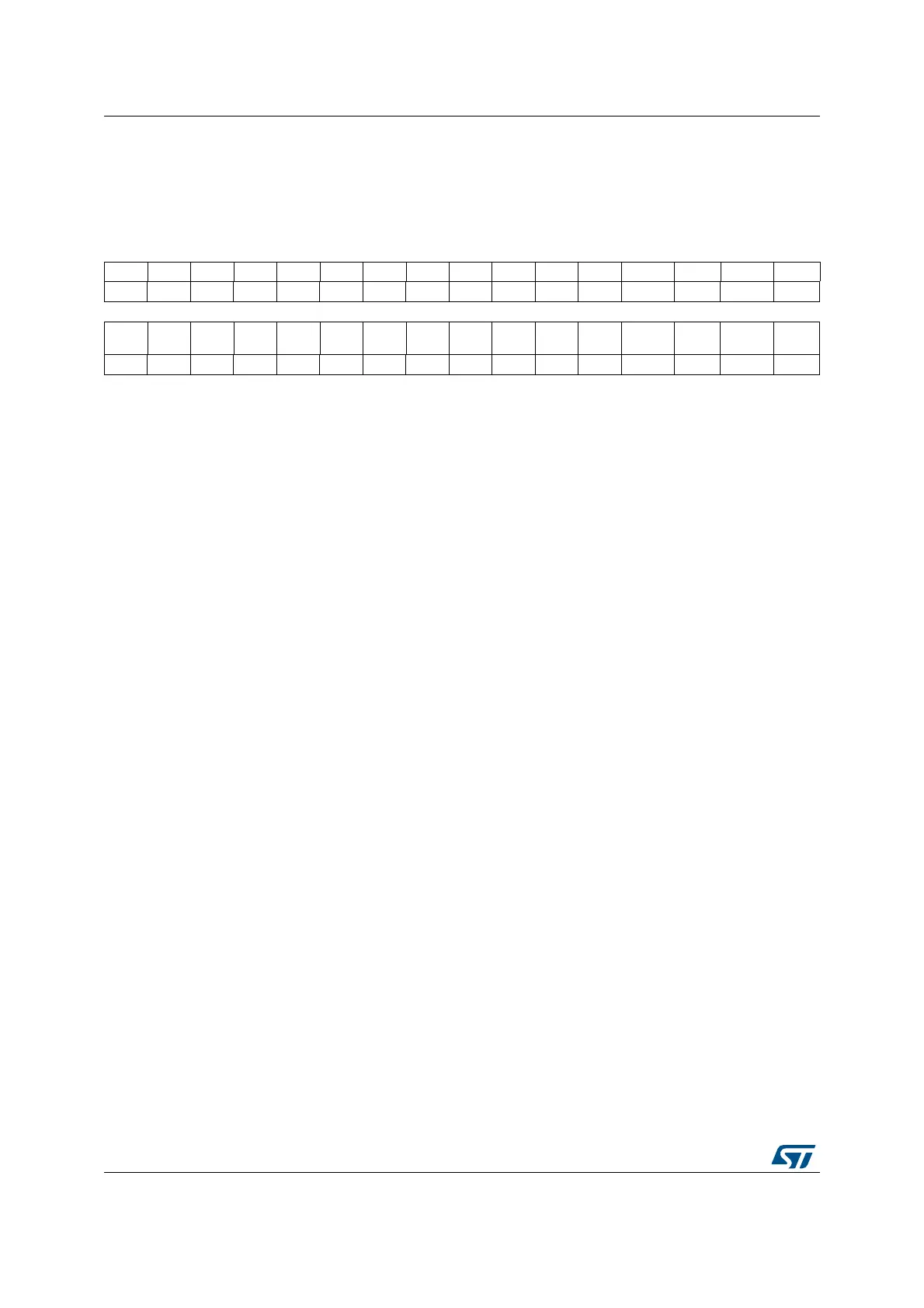

8.7.4 CRS interrupt flag clear register (CRS_ICR)

Address offset: 0x0C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

151413121110987654 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. ESYNCC ERRC

SYNC

WARNC

SYNC

OKC

rw rw rw rw

Bits 31:4 Reserved, must be kept at reset value.

Bit 3 ESYNCC: Expected SYNC clear flag

Writing 1 to this bit clears the ESYNCF flag in the CRS_ISR register.

Bit 2 ERRC: Error clear flag

Writing 1 to this bit clears TRIMOVF, SYNCMISS and SYNCERR bits and consequently also

the ERRF flag in the CRS_ISR register.

Bit 1 SYNCWARNC: SYNC warning clear flag

Writing 1 to this bit clears the SYNCWARNF flag in the CRS_ISR register.

Bit 0 SYNCOKC: SYNC event OK clear flag

Writing 1 to this bit clears the SYNCOKF flag in the CRS_ISR register.

Loading...

Loading...