Analog-to-digital converters (ADC) RM0440

720/2126 RM0440 Rev 4

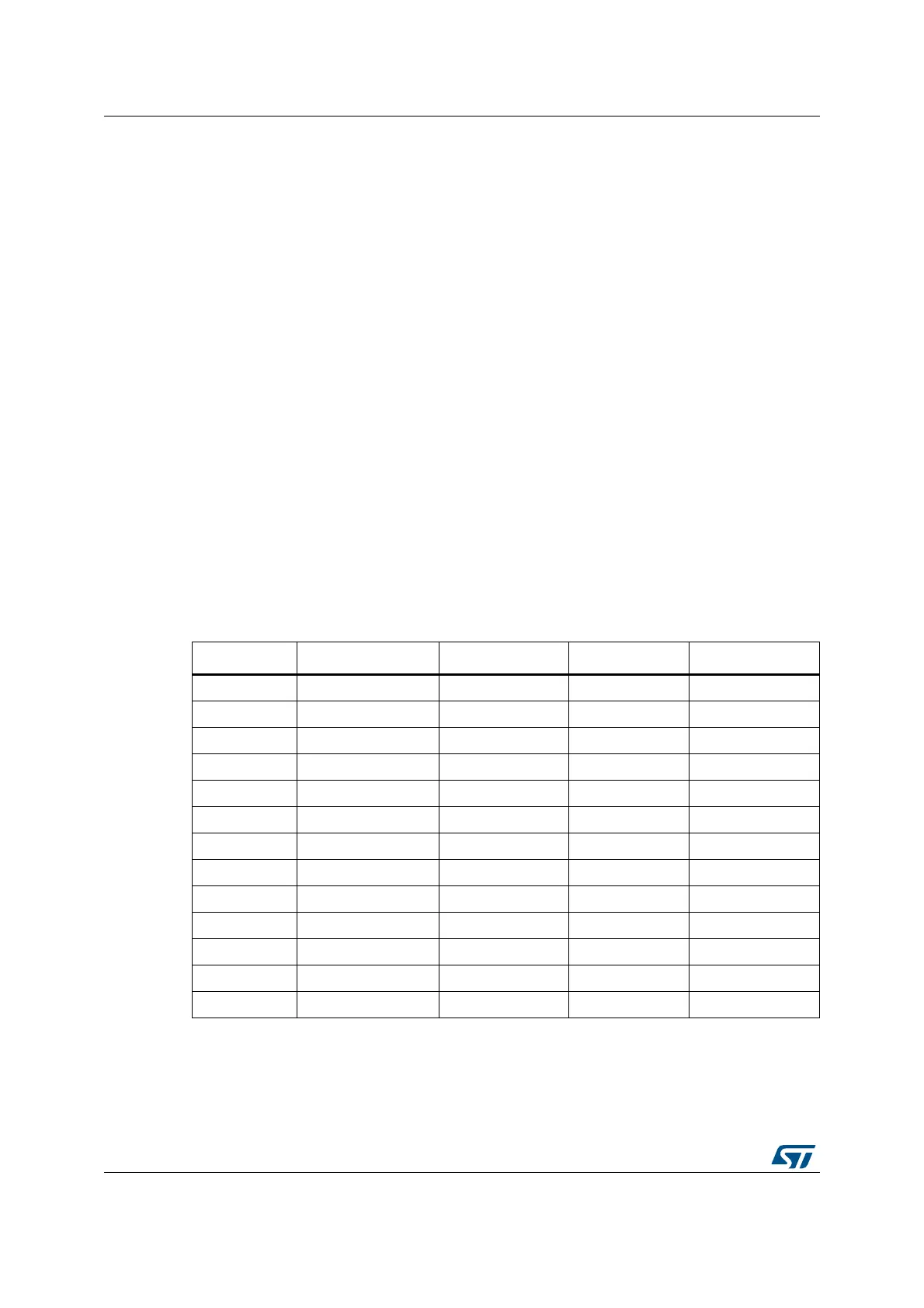

Bits 11:8 DELAY: Delay between 2 sampling phases

These bits are set and cleared by software. These bits are used in dual interleaved modes.

Refer to Table 175 for the value of ADC resolution versus DELAY bits values.

Note: The software is allowed to write these bits only when the ADCs are disabled

(ADCAL=0, JADSTART=0, ADSTART=0, ADSTP=0, ADDIS=0 and ADEN=0).

Bits 7:5 Reserved, must be kept at reset value.

Bits 4:0 DUAL[4:0]: Dual ADC mode selection

These bits are written by software to select the operating mode.

All the ADCs independent:

00000: Independent mode

00001 to 01001: Dual mode, master and slave ADCs working together

00001: Combined regular simultaneous + injected simultaneous mode

00010: Combined regular simultaneous + alternate trigger mode

00011: Combined Interleaved mode + injected simultaneous mode

00100: Reserved

00101: Injected simultaneous mode only

00110: Regular simultaneous mode only

00111: Interleaved mode only

01001: Alternate trigger mode only

All other combinations are reserved and must not be programmed

Note: The software is allowed to write these bits only when the ADCs are disabled

(ADCAL=0, JADSTART=0, ADSTART=0, ADSTP=0, ADDIS=0 and ADEN=0).

Table 175. DELAY bits versus ADC resolution

DELAY bits 12-bit resolution 10-bit resolution 8-bit resolution 6-bit resolution

0000 1 * T

adc_ker_ck

1 * T

adc_ker_ck

1 * T

adc_ker_ck

1 * T

adc_ker_ck

0001 2 * T

adc_ker_ck

2 * T

adc_ker_ck

2 * T

adc_ker_ck

2 * T

adc_ker_ck

0010 3 * T

adc_ker_ck

3 * T

adc_ker_ck

3 * T

adc_ker_ck

3 * T

adc_ker_ck

0011 4 * T

adc_ker_ck

4 * T

adc_ker_ck

4 * T

adc_ker_ck

4 * T

adc_ker_ck

0100 5 * T

adc_ker_ck

5 * T

adc_ker_ck

5 * T

adc_ker_ck

5 * T

adc_ker_ck

0101 6 * T

adc_ker_ck

6 * T

adc_ker_ck

6 * T

adc_ker_ck

6 * T

adc_ker_ck

0110 7 * T

adc_ker_ck

7 * T

adc_ker_ck

7 * T

adc_ker_ck

6 * T

adc_ker_ck

0111 8 * T

adc_ker_ck

8 * T

adc_ker_ck

8 * T

adc_ker_ck

6 * T

adc_ker_ck

1000 9 * T

adc_ker_ck

9 * T

adc_ker_ck

8 * T

adc_ker_ck

6 * T

adc_ker_ck

1001 10 * T

adc_ker_ck

10 * T

adc_ker_ck

8 * T

adc_ker_ck

6 * T

adc_ker_ck

1010 11 * T

adc_ker_ck

10 * T

adc_ker_ck

8 * T

adc_ker_ck

6 * T

adc_ker_ck

1011 12 * T

adc_ker_ck

10 * T

adc_ker_ck

8 * T

adc_ker_ck

6 * T

adc_ker_ck

others 12 * T

adc_ker_ck

10 * T

adc_ker_ck

8 * T

adc_ker_ck

6 * T

adc_ker_ck

Loading...

Loading...