Design Guide 215

Layout Checklist

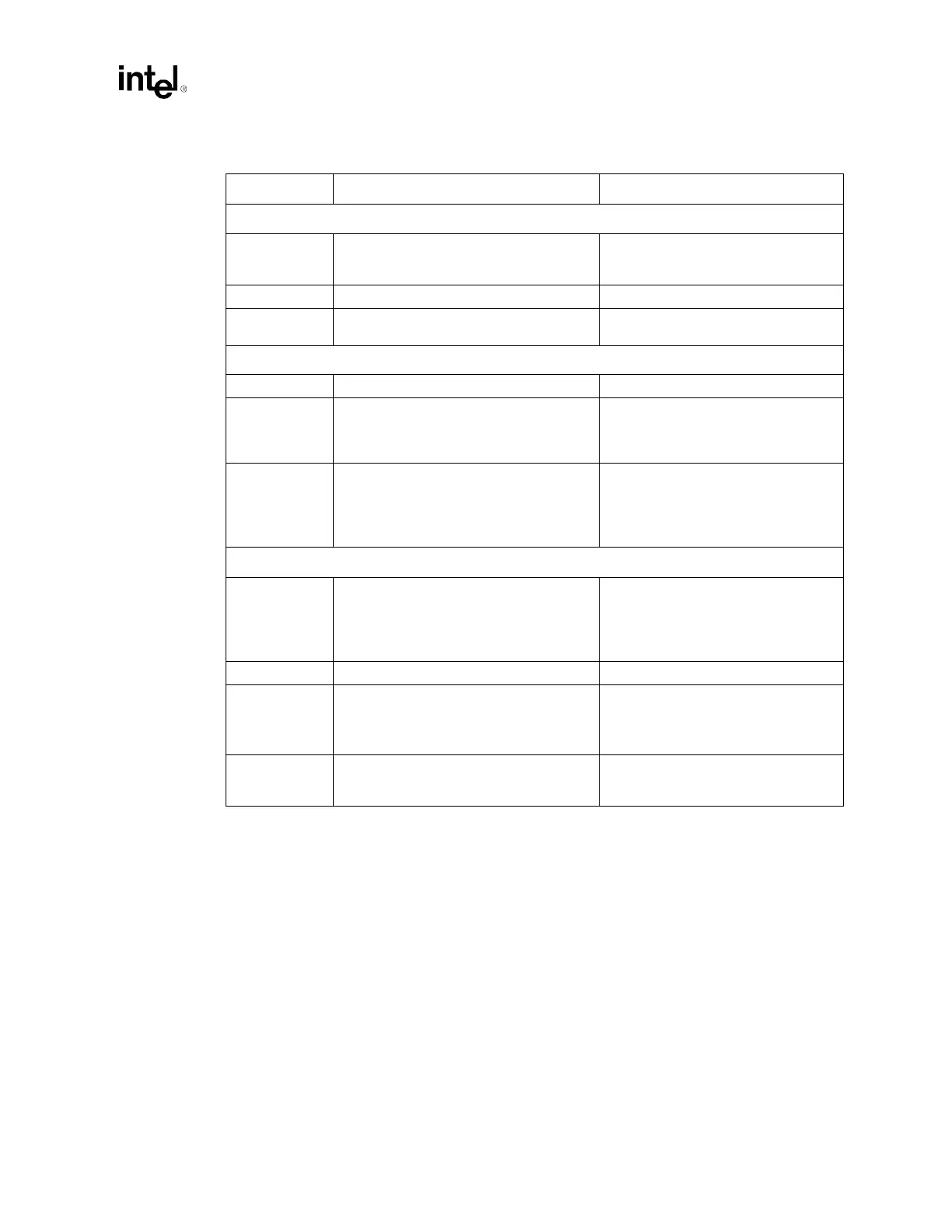

Clocks, Reset, Miscellaneous Signals

HCLKINP

HLCKINN

• HCLKs should be length matched to all

processors BCLKs. See Table 4-3 for

routing guidelines.

• Refer to Section 4.1.1.

CLK66 • Place series resistor close to CK408B. • Refer to Section 4.1.2.

RSTIN# • Connect to PCIRST# output of the

ICH3-S.

Miscellaneous Signals

XORMODE#

HIRCOMP_x

HIVREF[D:A]

HISWNG_[D:A]

• RCOMP, VOH, VOL, VSWING, VREF

resistor networks are no more then 1”

away from the MCH, and trace width is

greater than 15 mils.

• Refer to Section 7.2.2, Section 7.2.3,

Section 7.3.2, and Section 7.3.3.

HXRCOMP

HYRCOMP

• This signal is used to calibrate the

Host AGTL+ I/O buffers

characteristics to specific board

characteristic.

• Refer to Section 5.3.5.

Voltage References – Power Planes

HDVREF[3:0]

HAVREF[1:0]

HCCVREF

• Use one dedicated voltage divider for all

these signals. Decouple the voltage

divider with a 1 µF capacitor.

• To provide constant and clean power

delivery to the data, address, and

common clock signals of the host

AGTL+ interface.

• Refer to Section 12.2.10.

VREF_DDR[5:0] • Refer to Section 6.8.

HXSWING

HYSWING

• The HXSWING and HYSWING inputs

of MCH are used to provide reference

voltage for the compensation logic.

• Refer to Section 5.3.5.

VCCA • High frequency decoupling for VCCA

planes is located as close as possible to

the associated MCH ball.

NOTES:

1. The BREQ0# pin on the MCH corresponds to the BR0# pin on the processor.

2. The CPURST# pin on the MCH corresponds to the RESET# pin on the processor.

3. HA[35:3]# pins on the MCH correspond to A[35:3]# pins on the processor.

4. HD[63:0]# pins on the MCH correspond to D[63:0]# pins on the processor.

5. HADSTB[1:0]# pins on the MCH correspond to ADSTB[1:0]# pins on the processor.

6. HADSTBN[3:0]# pins on the MCH correspond to DSTBN[3:0]# pins on the processor.

7. HADSTBP[3:0]# pins on the MCH correspond to DSTBP[3:0]# pins on the processor.

8. HREQ[4:0]# pins on the MCH correspond to REQ[4:0]# pins on the processor.

9. The HTRDY# pin on the MCH corresponds to the TRDY# pin on the processor.

10.The MCH XERR# pin can be connected to the processor IERR# pin or the processor MCERR# pin.

Table 14-2. MCH Layout Checklist (Sheet 3 of 3)

Checklist Items Recommendations Comments

Loading...

Loading...