RM0440 Rev 4 1853/2126

RM0440 Serial audio interface (SAI)

1858

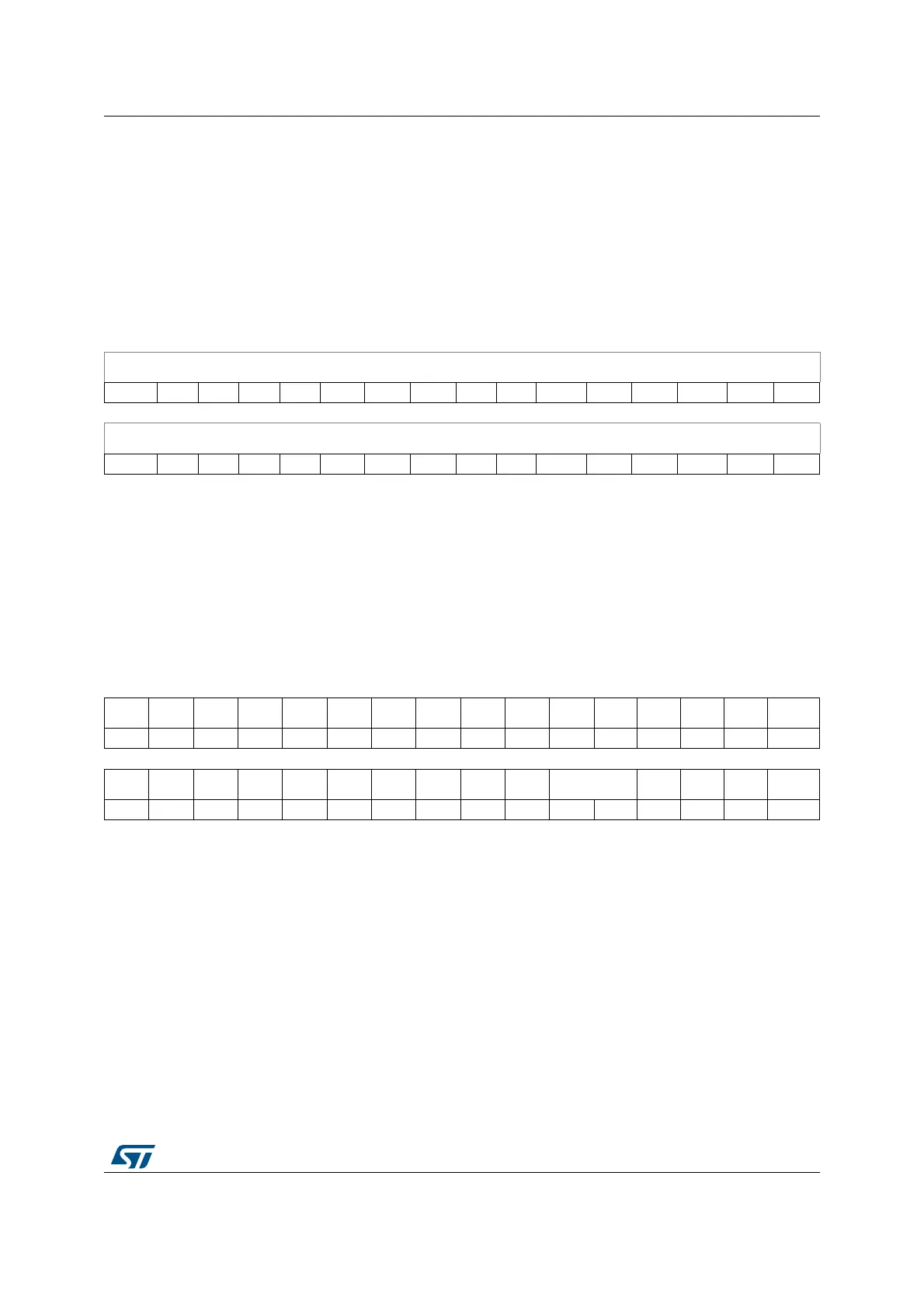

40.5.16 SAI data register (SAI_BDR)

Address offset: 0x040

Reset value: 0x0000 0000

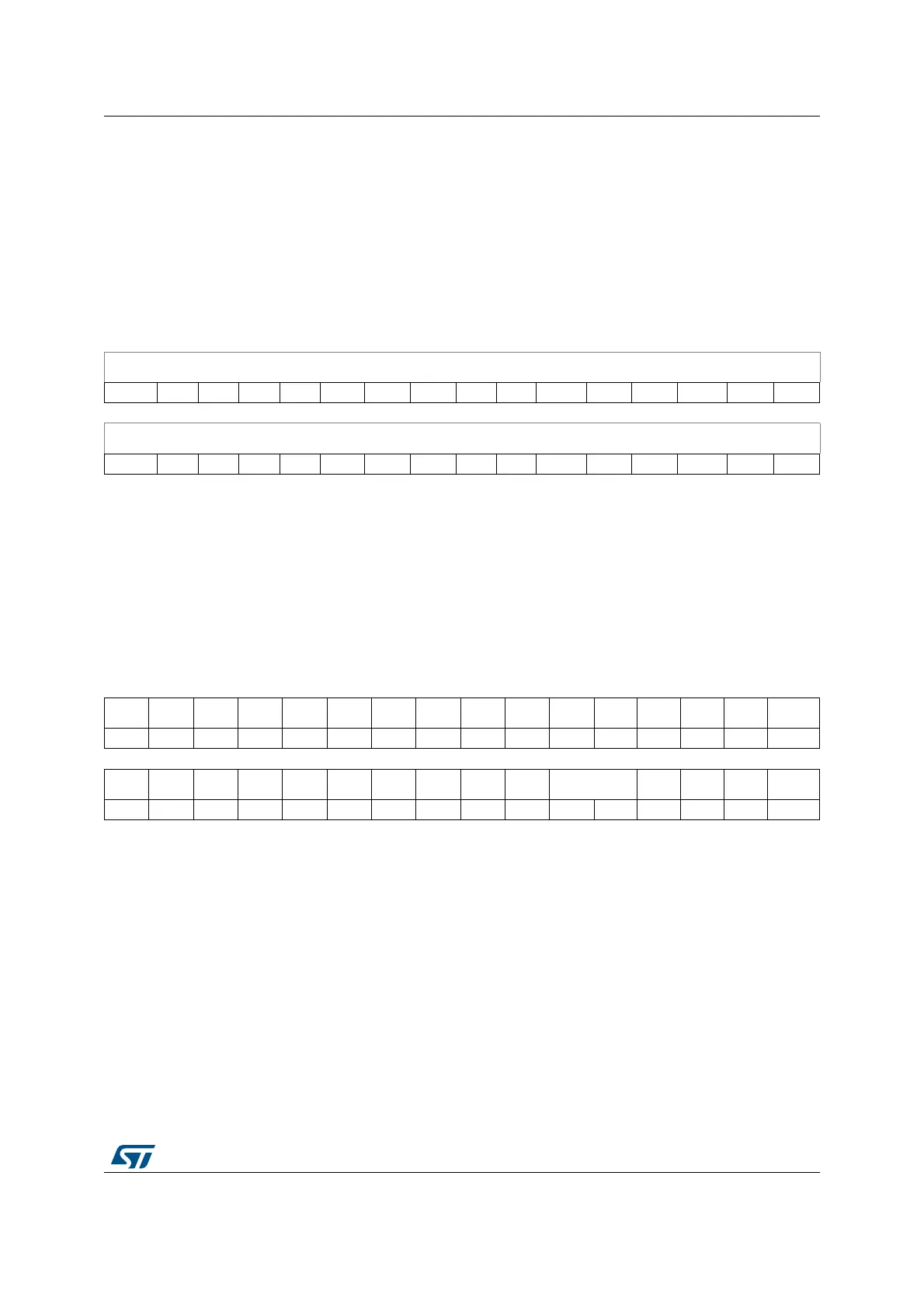

40.5.17 SAI PDM control register (SAI_PDMCR)

Address offset: 0x0044

Reset value: 0x0000 0000

Bits 31:0 DATA[31:0]: Data

A write to this register loads the FIFO provided the FIFO is not full.

A read from this register empties the FIFO if the FIFO is not empty.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DATA[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DATA[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 DATA[31:0]: Data

A write to this register loads the FIFO provided the FIFO is not full.

A read from this register empties the FIFO if the FIFO is not empty.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. CKEN4 CKEN3 CKEN2 CKEN1 Res. Res. MICNBR[1:0] Res. Res. Res. PDMEN

rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:12 Reserved, must be kept at reset value.

Bit 11 CKEN4: Clock enable of bitstream clock number 4

This bit is set and cleared by software.

0: SAI_CK4 clock disabled

1: SAI_CK4 clock enabled

Note: It is not recommended to configure this bit when PDMEN = 1.

Loading...

Loading...