RM0440 Rev 4 841/2126

RM0440 True random number generator (RNG)

843

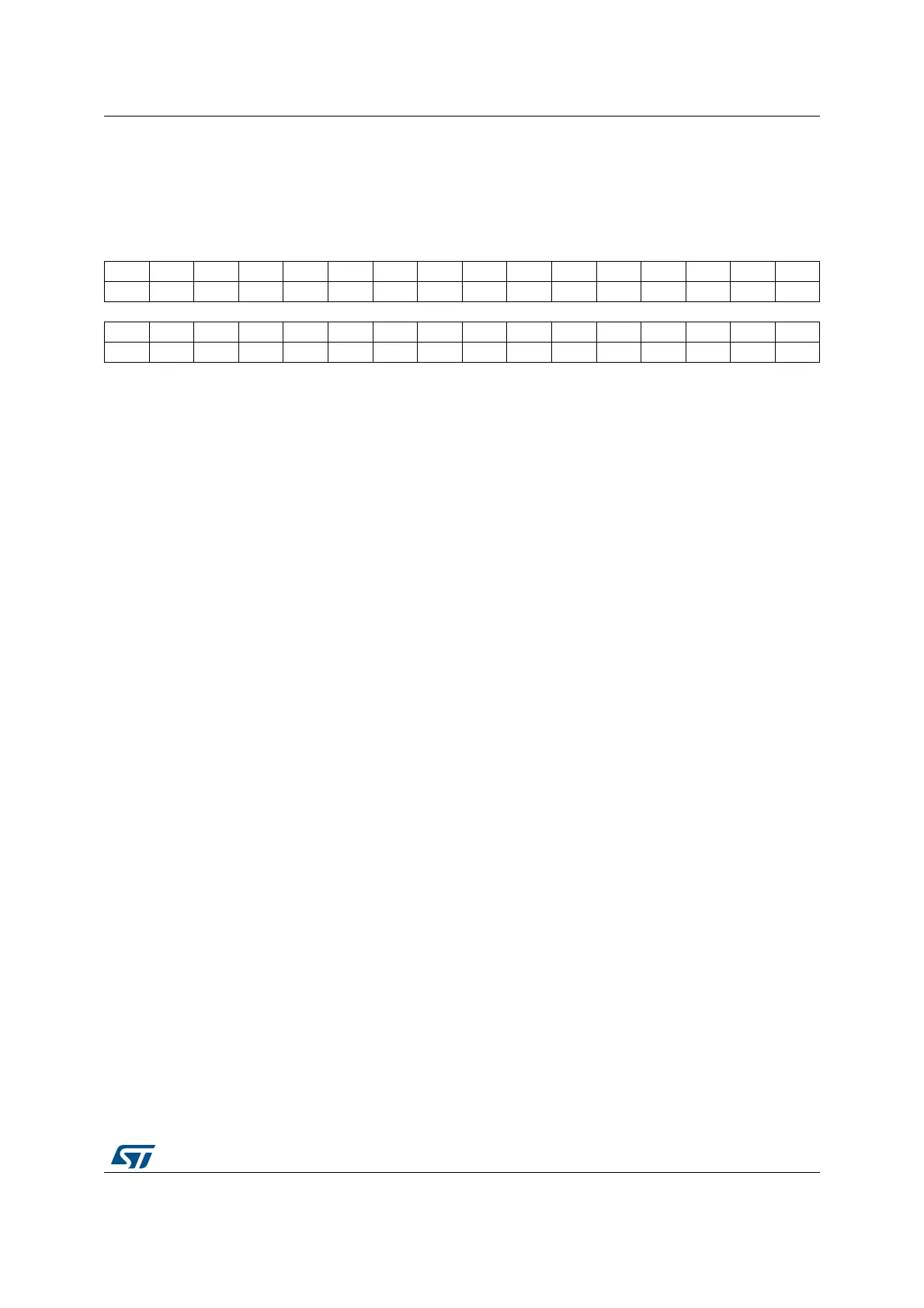

26.7.2 RNG status register (RNG_SR)

Address offset: 0x004

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

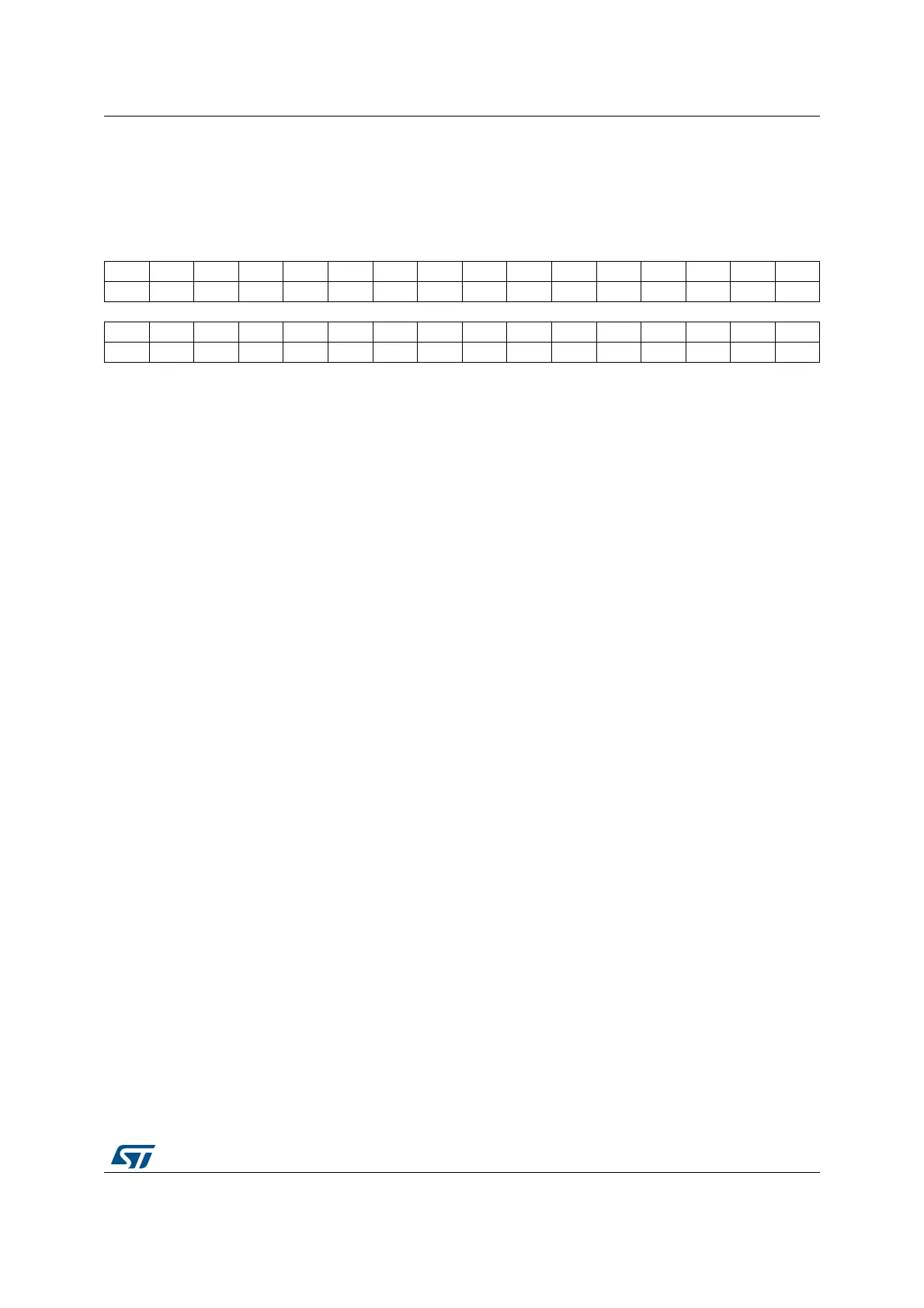

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. SEIS CEIS Res. Res. SECS CECS DRDY

rc_w0 rc_w0 r r r

Bits 31:7 Reserved, must be kept at reset value.

Bit 6 SEIS: Seed error interrupt status

This bit is set at the same time as SECS. It is cleared by writing 0. Writing 1 has no effect.

0: No faulty sequence detected

1: At least one faulty sequence has been detected. See SECS bit description for details.

An interrupt is pending if IE = 1 in the RNG_CR register.

Bit 5 CEIS: Clock error interrupt status

This bit is set at the same time as CECS. It is cleared by writing 0. Writing 1 has no effect.

0: The RNG clock is correct (fRNGCLK> fHCLK/32)

1: The RNG has been detected too slow (fRNGCLK< fHCLK/32)

An interrupt is pending if IE = 1 in the RNG_CR register.

Bits 4:3 Reserved, must be kept at reset value.

Bit 2 SECS: Seed error current status

0: No faulty sequence has currently been detected. If the SEIS bit is set, this means that a

faulty sequence was detected and the situation has been recovered.

1: At least one of the following faulty sequence has been detected:

– One of the noise source has provided more than 64 consecutive bits at a constant

value (“0” or “1”), or more than 32 consecutive occurrence of two bit patterns (“01”

or “10”)

– Both noise sources have delivered more than 32 consecutive bits at a constant

value (“0” or “1”), or more than 16 consecutive occurrence of two bit patterns (“01”

or “10”)

Bit 1 CECS: Clock error current status

0: The RNG clock is correct (fRNGCLK> fHCLK/32). If the CEIS bit is set, this means that a

slow clock was detected and the situation has been recovered.

1: The RNG clock is too slow (fRNGCLK< fHCLK/32).

Note: CECS bit is valid only if the CED bit in the RNG_CR register is set to 0.

Bit 0 DRDY: Data Ready

0: The RNG_DR register is not yet valid, no random data is available.

1: The RNG_DR register contains valid random data.

Once the output buffer becomes empty (after reading the RNG_DR register), this bit returns to

0 until a new random value is generated.

Note: The DRDY bit can rise when the peripheral is disabled (RNGEN=0 in the RNG_CR

register).

If IE=1 in the RNG_CR register, an interrupt is generated when DRDY=1.

Loading...

Loading...