Peripherals interconnect matrix RM0440

388/2126 RM0440 Rev 4

11.3.3 From ADC (ADCx) to timer (TIMx, HRTIM)

See please Table 73: Interconnect 2 and Table 81.: Interconnect 10

ADCs Analog watchdogs are connected to TIM1/8/20 for digital power applications (cycle-

bycycle current regulation with ADC).

A description of the ADC analog watchdog setting is provided in: Section 21.4.28: Analog

window watchdog (AWD1EN, JAWD1EN, AWD1SGL, AWD1CH, AWD2CH, AWD3CH,

AWD_HTx, AWD_LTx, AWDx).

Trigger settings on the timer are provided in: Section 28.3.6: External trigger input.

Triggering signals

The output (from ADC) is on signals ADCn_AWDx_OUT and the input (to timer) on signal

TIMx_ETR (external trigger) or hrtim_eevx[4:1].

Active power mode

Run, Sleep, Low-power run, Low-power sleep.

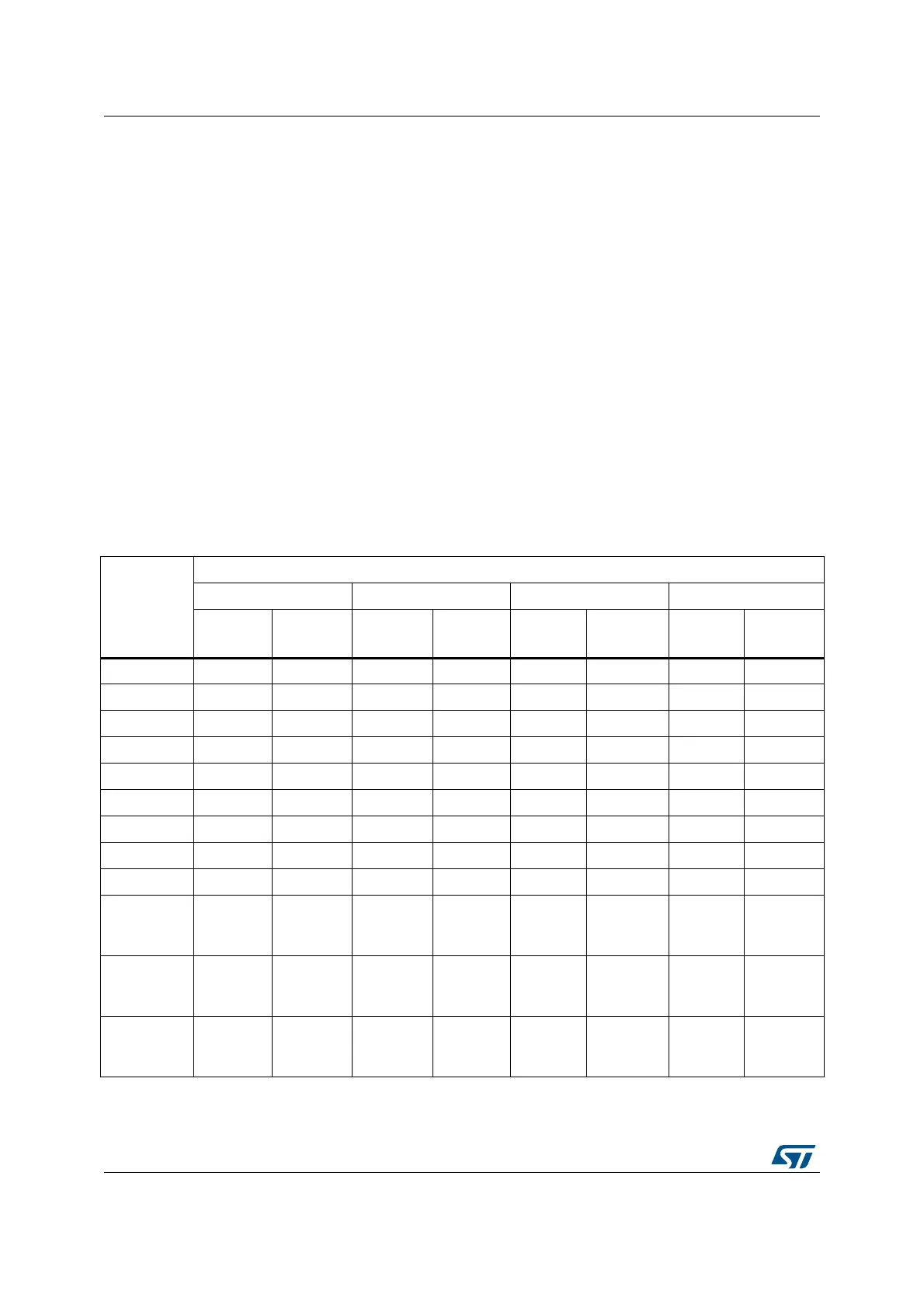

11.3.4 From timer (TIMx, HRTIM) and EXTI to DAC (DACx)

Table 66. Interconnect 20

DAC trigger

selection

(TSELx[3:0],

STRSTTRIG

SELx[3:0])

DAC triggers signals assignment

DAC1 DAC2 DAC3 DAC4

Update/

reset

Inc

Update/

reset

Inc

Update

/reset

Inc

Update/

reset

Inc

0 sw - sw - sw - sw -

1 tim8_trgo tim8_trgo tim8_trgo tim8_trgo tim1_trgo tim1_trgo tim8_trgo tim8_trgo

2 tim7_trgo tim7_trgo tim7_trgo tim7_trgo tim7_trgo tim7_trgo tim7_trgo tim7_trgo

3 tim15_trgo tim15_trgo tim15_trgo tim15_trgo tim15_trgo tim15_trgo tim15_trgo tim15_trgo

4 tim2_trgo tim2_trgo tim2_trgo tim2_trgo tim2_trgo tim2_trgo tim2_trgo tim2_trgo

5 tim4_trgo tim4_trgo tim4_trgo tim4_trgo tim4_trgo tim4_trgo tim4_trgo tim4_trgo

6 exti9 exti10 exti9 exti10 exti9 exti10 exti9 exti10

7 tim6_trgo tim6_trgo tim6_trgo tim6_trgo tim6_trgo tim6_trgo tim6_trgo tim6_trgo

8 tim3_trgo tim3_trgo tim3_trgo tim3_trgo tim3_trgo tim3_trgo tim3_trgo tim3_trgo

9

hrtim_dac_

reset_trg1

hrtim_step

_trig1

hrtim_dac_

reset_trg1

hrtim_step

_trig1

hrtim_dac

_reset_trg

1

hrtim_step

_trig1

hrtim_dac

_reset_trg

1

hrtim_step

_trig1

10

hrtim_dac_

reset_trg2

hrtim_step

_trig2

hrtim_dac_

reset_trg2

hrtim_step

_trig2

hrtim_dac

_reset_trg

2

hrtim_stept

rig_2

hrtim_rst_

_trig_2

hrtim_step

_trig2

11

hrtim_dac_

reset_trg3

hrtim_step

_trig3

hrtim_dac_

reset_trg3

hrtim_step

_trig3

hrtim_dac

_reset_trg

3

hrtim_step

_trig3

hrtim_dac

_reset_trg

3

hrtim_step

_trig3

Loading...

Loading...