DMA request multiplexer (DMAMUX) RM0440

436/2126 RM0440 Rev 4

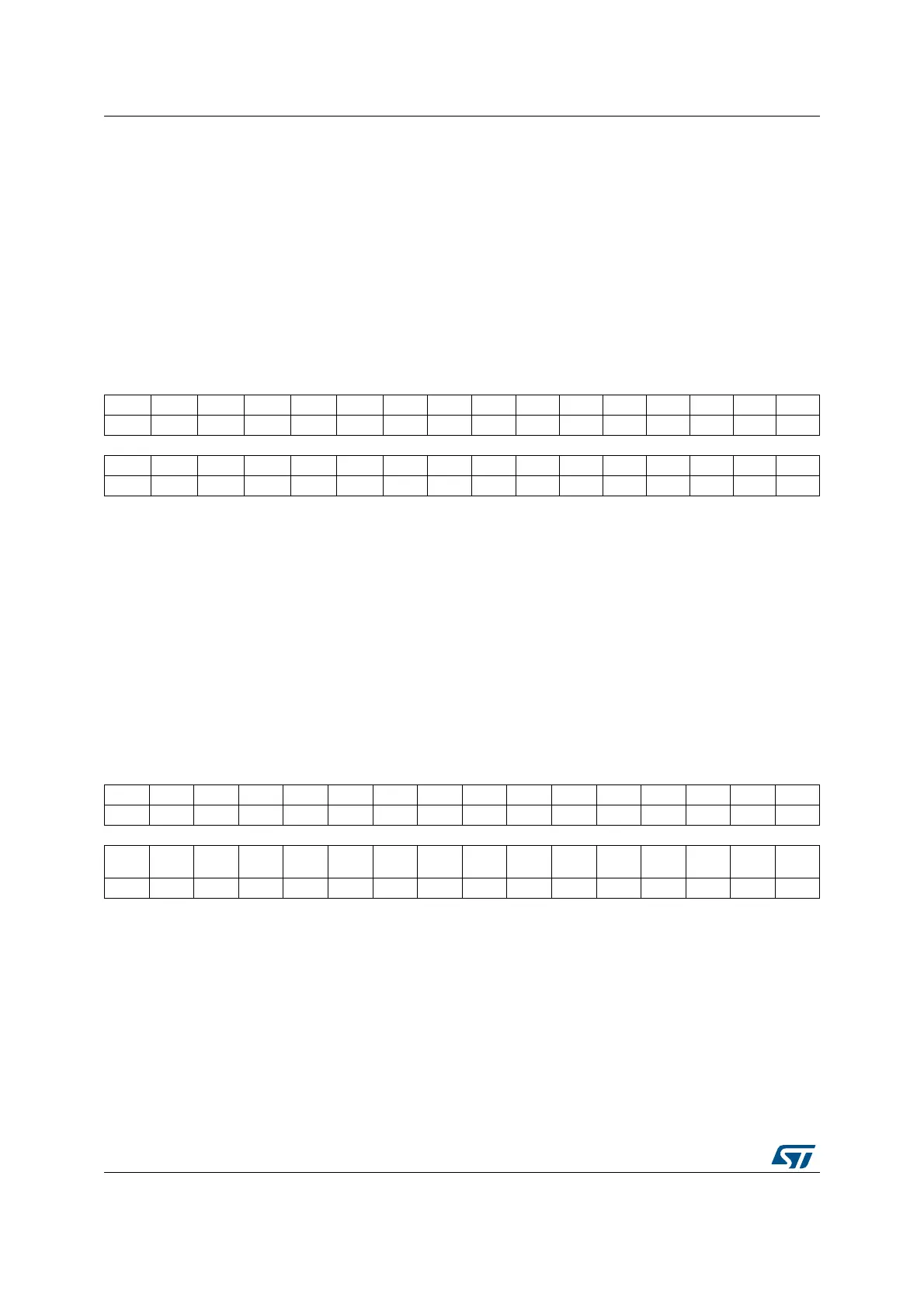

13.6.2 DMAMUX request line multiplexer interrupt channel status register

(DMAMUX_CSR)

Address offset: 0x080

Reset value: 0x0000 0000

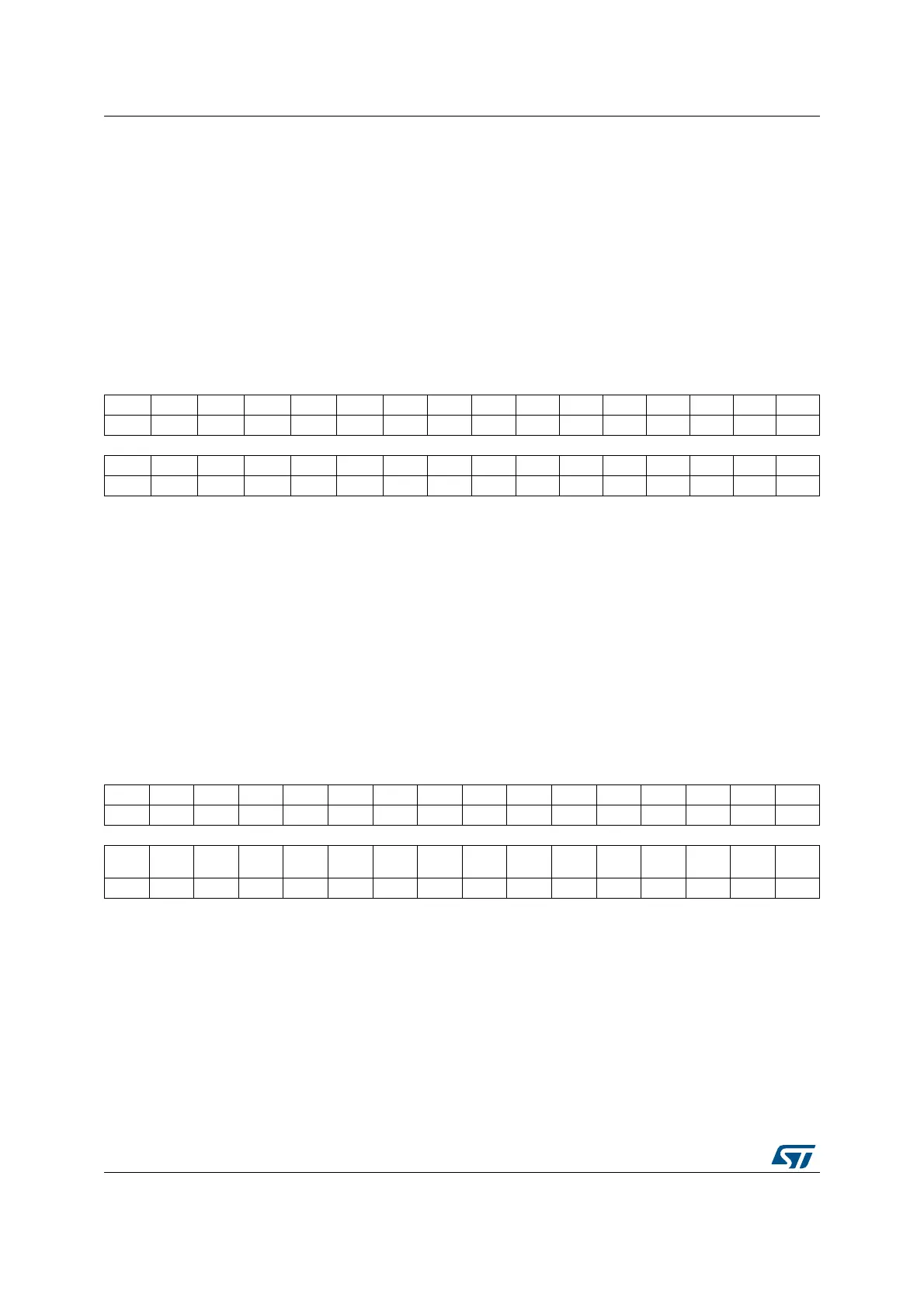

13.6.3 DMAMUX request line multiplexer interrupt clear flag register

(DMAMUX_CFR)

Address offset: 0x084

Reset value: 0x0000 0000

Bit 7 Reserved, must be kept at reset value.

Bits 6:0 DMAREQ_ID[6:0]: DMA request identification

Selects the input DMA request. See the DMAMUX table about assignments of multiplexer

inputs to resources.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SOF15 SOF14 SOF13 SOF12 SOF11 SOF10 SOF9 SOF8 SOF7 SOF6 SOF5 SOF4 SOF3 SOF2 SOF1 SOF0

rrrrrrrrrrrrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 SOF[15:0]: Synchronization overrun event flag

The flag is set when a synchronization event occurs on a DMA request line multiplexer

channel x, while the DMA request counter value is lower than NBREQ.

The flag is cleared by writing 1 to the corresponding CSOFx bit in DMAMUX_CFR register.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

CSOF

15

CSOF

14

CSOF

13

CSOF

12

CSOF

11

CSOF

10

CSOF

9

CSOF

8

CSOF

7

CSOF

6

CSOF

5

CSOF

4

CSOF

3

CSOF

2

CSOF

1

CSOF

0

wwwwwwwwwwwwwwww

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 CSOF[15:0]: Clear synchronization overrun event flag

Writing 1 in each bit clears the corresponding overrun flag SOFx in the DMAMUX_CSR

register.

Loading...

Loading...