STC8A8K64D4 Series Manual

-

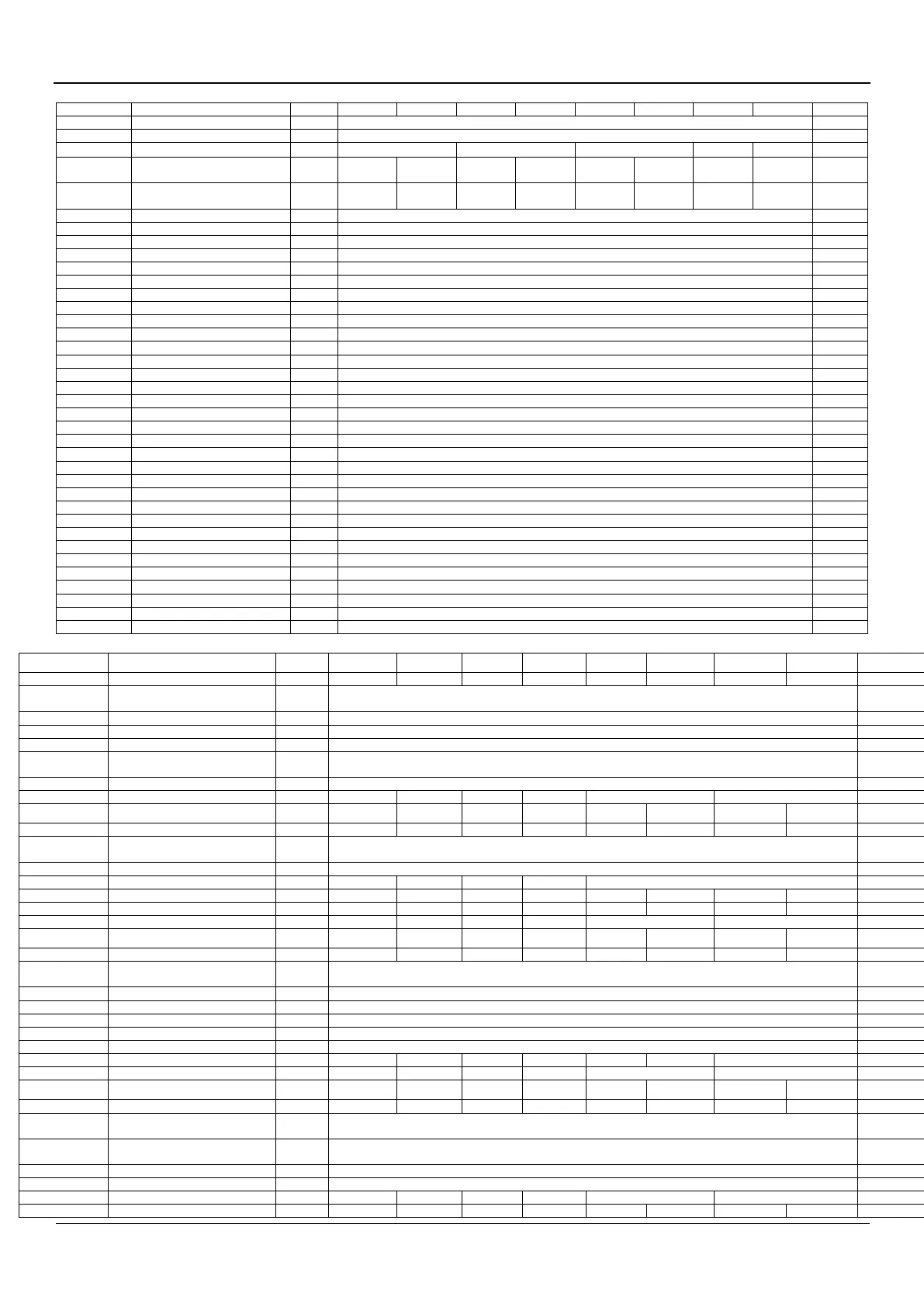

PCA3 Mode Control Register

I/O port interrupt priority low

register

I/O port interrupt priority high

register

M2M_DMA total bytes to be

transferred

M2M_DMA transfer completed bytes

M2M_DMA send address high byte

M2M_DMA send address low byte

M2M_DMA receive address high

byte

M2M_DMA receive address low byte

ADC_DMA configuration register

ADC_DMA receive address high

byte

ADC_DMA receive address low byte

ADC_DMA configuration register 2

SPI_DMA configuration register

SPI_DMA total bytes to be

transferred

SPI_DMA transfer completed bytes

SPI_DMA send address high byte

SPI_DMA send address low byte

SPI_DMA receive address high byte

SPI_DMA receive address low byte

SPI_DMA configuration register 2

UR1T_DMA configuration register

UR1T_DMA control register

UR1T_DMA total bytes to be

transferred

UR1T_DMA transfer completed

bytes

UR1T_DMA send address high byte

UR1T_DMA send address low byte

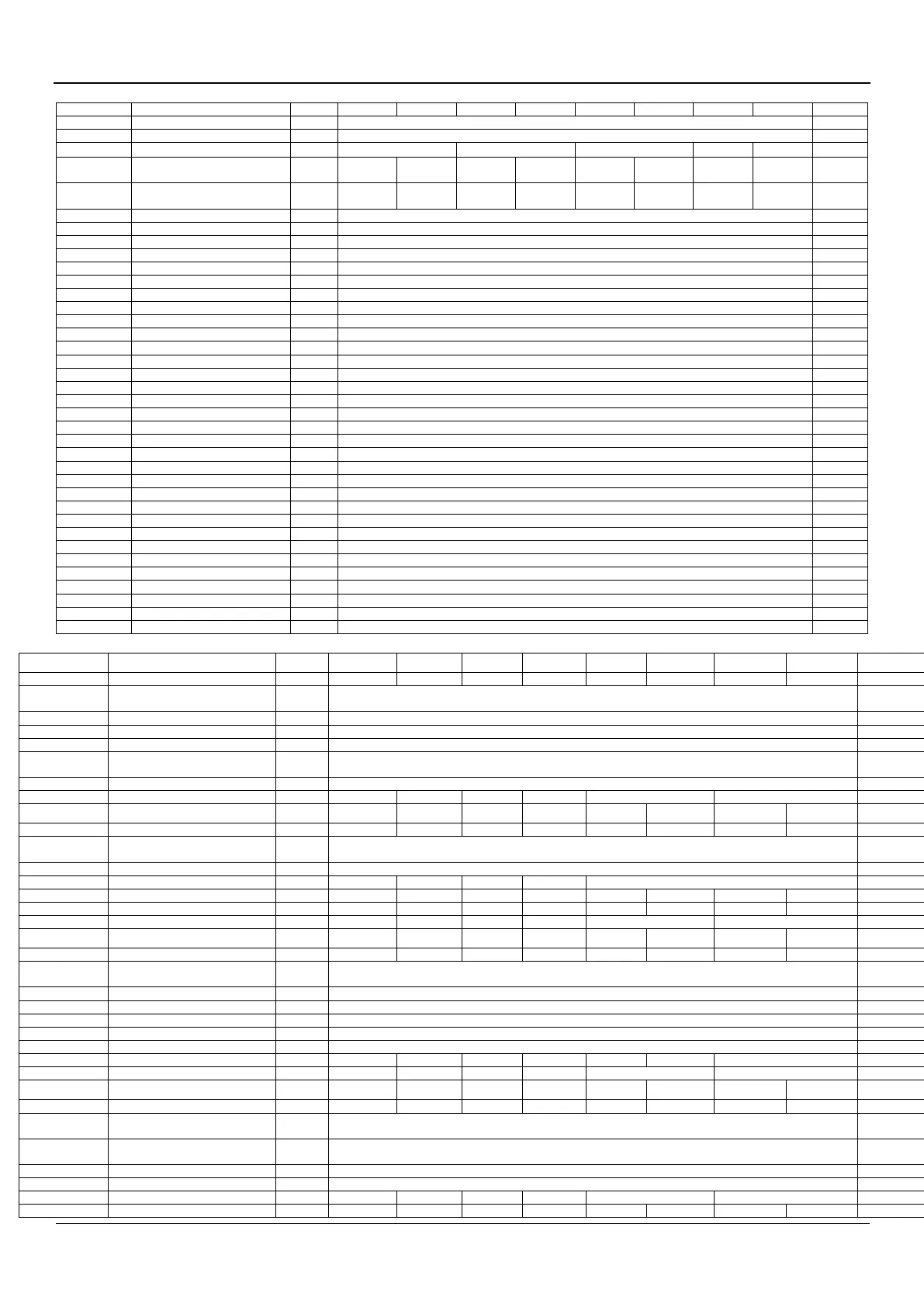

UR1R_DMA configuration register

UR1R_DMA control register

Loading...

Loading...