STC8A8K64D4 Series Manual

During EEPROM being read operation, the EEPROM data be read after the command execution is completed is

stored in the IAP_DATA register. When writing the EEPROM, the data to be written must be stored in the IAP_DATA

register before the write command is sent. The erase EEPROM command is not related to the IAP_DATA register.

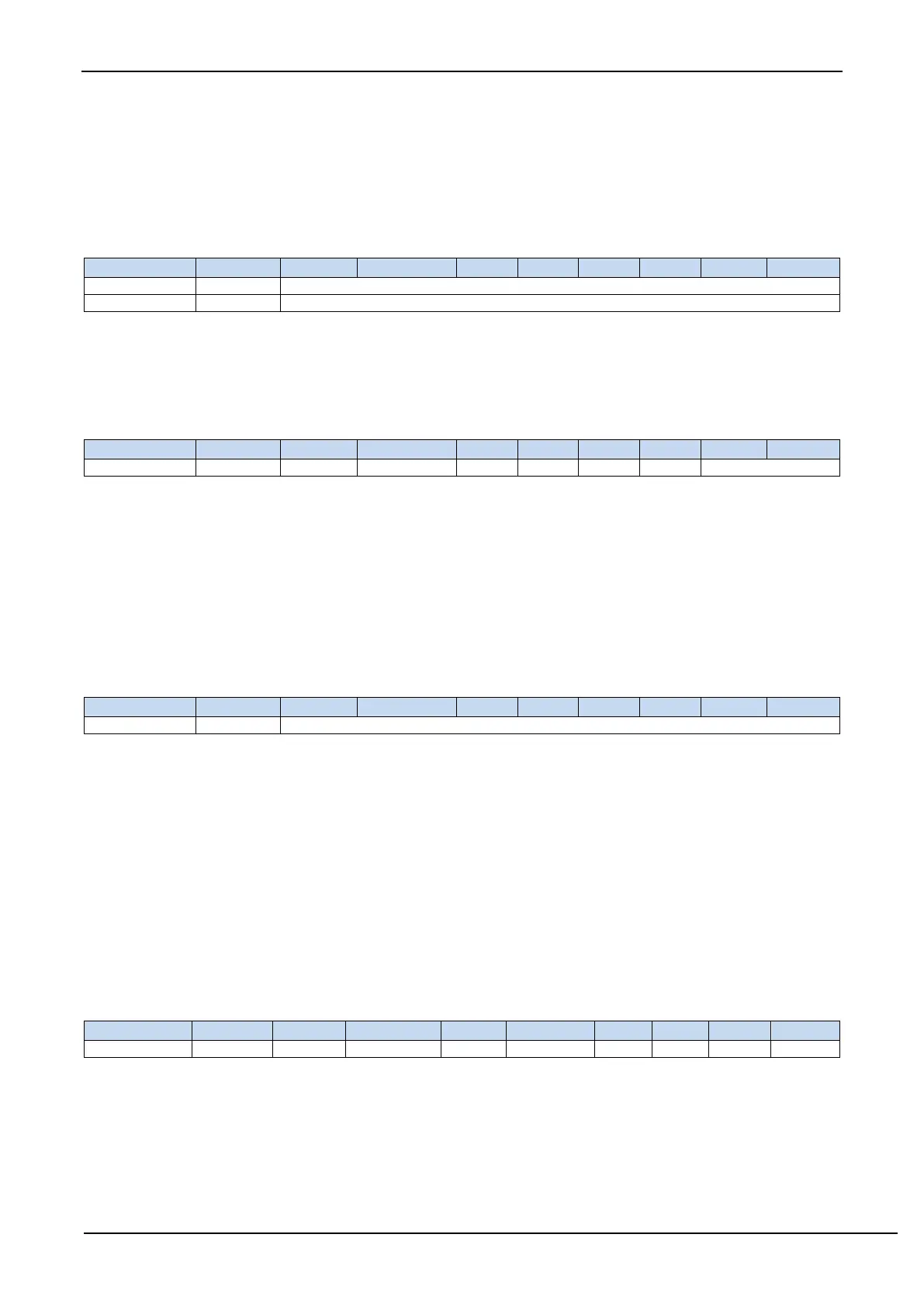

16.2.2 EEPROM address registers (IAP_ADDR)

The target address register of EEPROM for reading, writing and erasing operation. IAP_ADDRH is the high byte

address, and IAP_ADDRL is the low byte of the address.

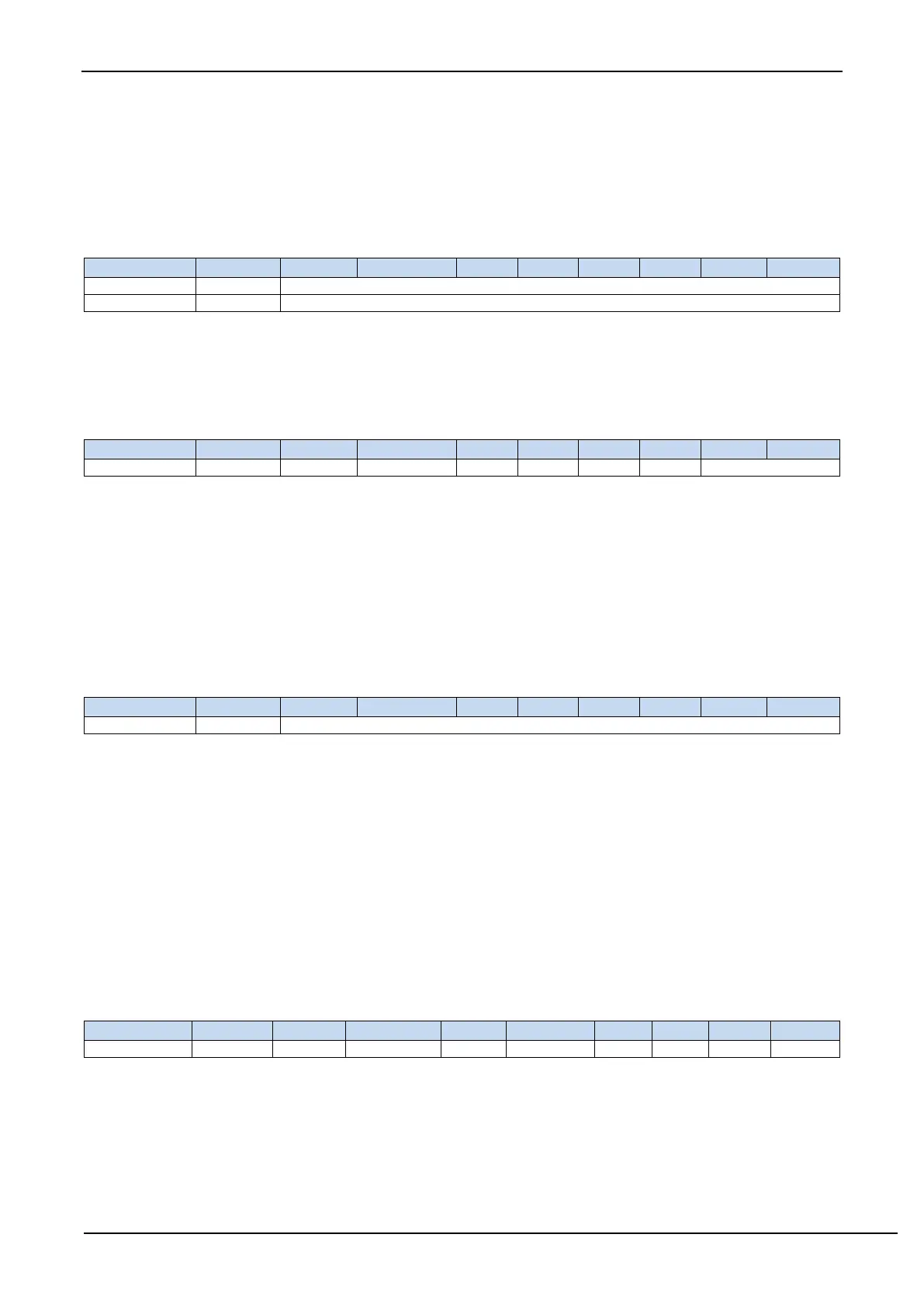

16.2.3 EEPROM command register (IAP_CMD)

CMD[1:0]: EEPROM operation command to be sent.

00: No operation.

01: EEPROM reading command. Read one byte from the destination address. Note: Writing operations can only

write 1 as 0 in the destination byte, not 0 as 1. Generally, when the target byte is not FFH, it must be erased first.

10: EEPROM writing command. Write one byte from the destination address.

11: EEPROM erasing command. Write one sector from the destination address. Note: The erase operation will

erase 1 sector (512 bytes) at a time, and the content of the entire sector will become FFH.

16.2.4 EEPROM trigger register (IAP_TRIG)

After setting the command register, address register, data register and control register of EEPROM for reading,

writing and erasing operation, 5AH and A5H are written to the trigger register IAP_TRIG sequentially to trigger the

corresponding operation. The order of 5AH and A5H can not be changed. After the operation is completed, the contents

of the EEPROM address registers IAP_ADDRH, IAP_ADDRL and the EEPROM command register IAP_CMD do not

change. The value of the IAP_ADDRH and IAP_ADDRL registers must be updated manually if the datum of the next

address needs to be operated.

Note: For every EEPROM operation, 5AH should be written to IAP_TRIG firstly and then A5H to take effect the

corresponding command. After the trigger command has been written, the CPU is in IDLE state until the corresponding

IAP operation completes. And then the CPU will return to the normal state from the IDLE and resume executing the

CPU instructions.

16.2.5 EEPROM control register (IAP_CONTR)

IAPEN: EEPROM operation enable control bit.

0: disable EEPROM operation.

1: Enable EEPROM operation.

SWBS: Software reset selection control bit, which should be used with SWRST.

0: Execute the program from the user code area after the software reset.

1: Execute the program from the ISP memory area after the software reset.

Loading...

Loading...