PWMTADCH: the upper 7 bits of the PWM triggers ADC time.

PWMTADCL: the lower 8 bits of the PWM triggers ADC time.

If EPWMTA =1 and ADC_POWER=1, {PWMTADCH, PWMTADCL} forms a 15-bit register. In the PWM counting

cycle, the hardware will trigger A/D conversion automatically when the internal PWM counting value equals to

the value of {PWMTADCH, PWMTADCL}.

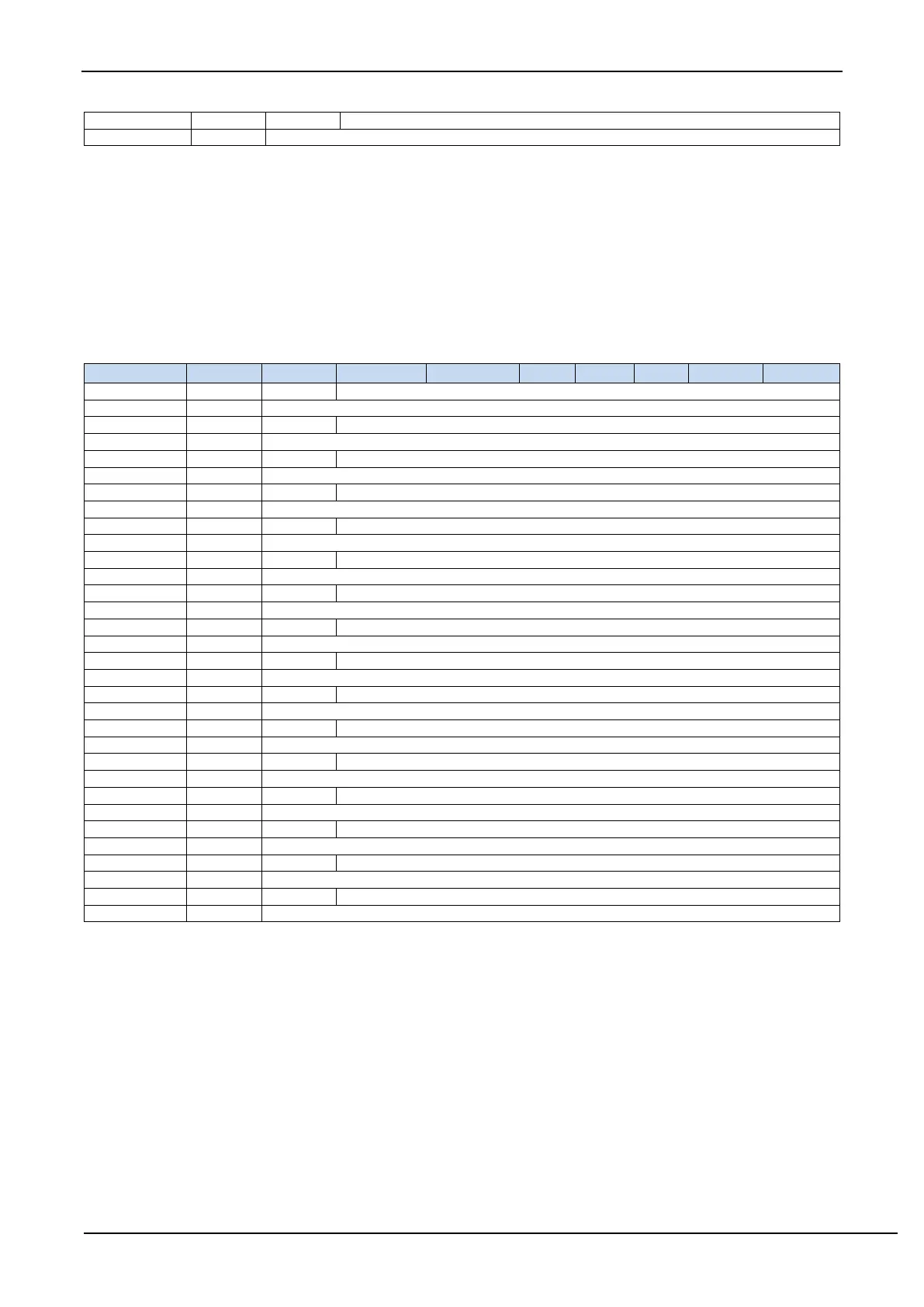

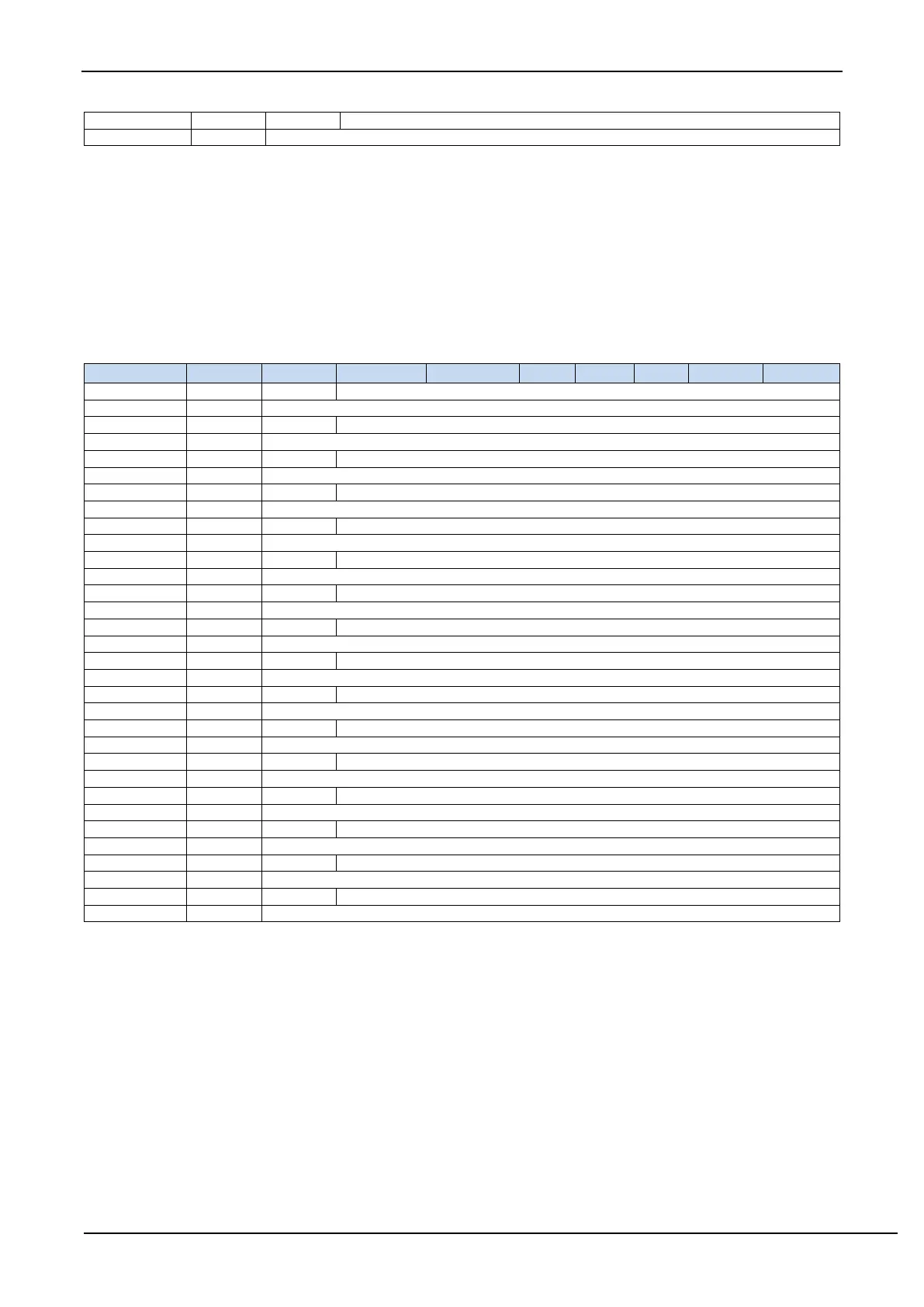

19.2.8 PWM Level output setting count value Registers (PWMnT1,

PWMnT2)

PWMiT1H: The upper 7 bits of T1 counter value of channel i of PWM. (i= 0~7)

PWMiT1L: The lower 8 bits of T1 counter value of channel i of PWM. (i= 0~7)

PWMiT2H: The upper 7 bits of T2 counter value of channel i of PWM. (i= 0~7)

PWMiT2L: The lower 8 bits of T2counter value of channel i of PWM. (i= 0~7)

{PWMiT1H, PWMiT1L} and {PWMiT2H, PWMiT2L} of every channel of every PWM are combined into two 15-bit

registers, which are used to control the two flip points of the PWM output waveform in every PWM cycle of each

PWM. During the counting cycle of PWM, the output of PWM will be low level when the internal counting value

of PWMn is equal to the value of T1 set by{PWMiT1H, PWMiT1L}. And the output of the PWM will be high

level when the internal counting value of PWM is queal to the value of the T2 set by {PWMT2H, PWMT2L}.

Note: When the values of {PWMiT1H, PWMiT1L} and {PWMiT2H, PWMiT2L} are set equal, and if the internal

count value of PWM is equal to the set value of T1 / T2, it will output low level.

Loading...

Loading...