STC8A8K64D4 Series Manual

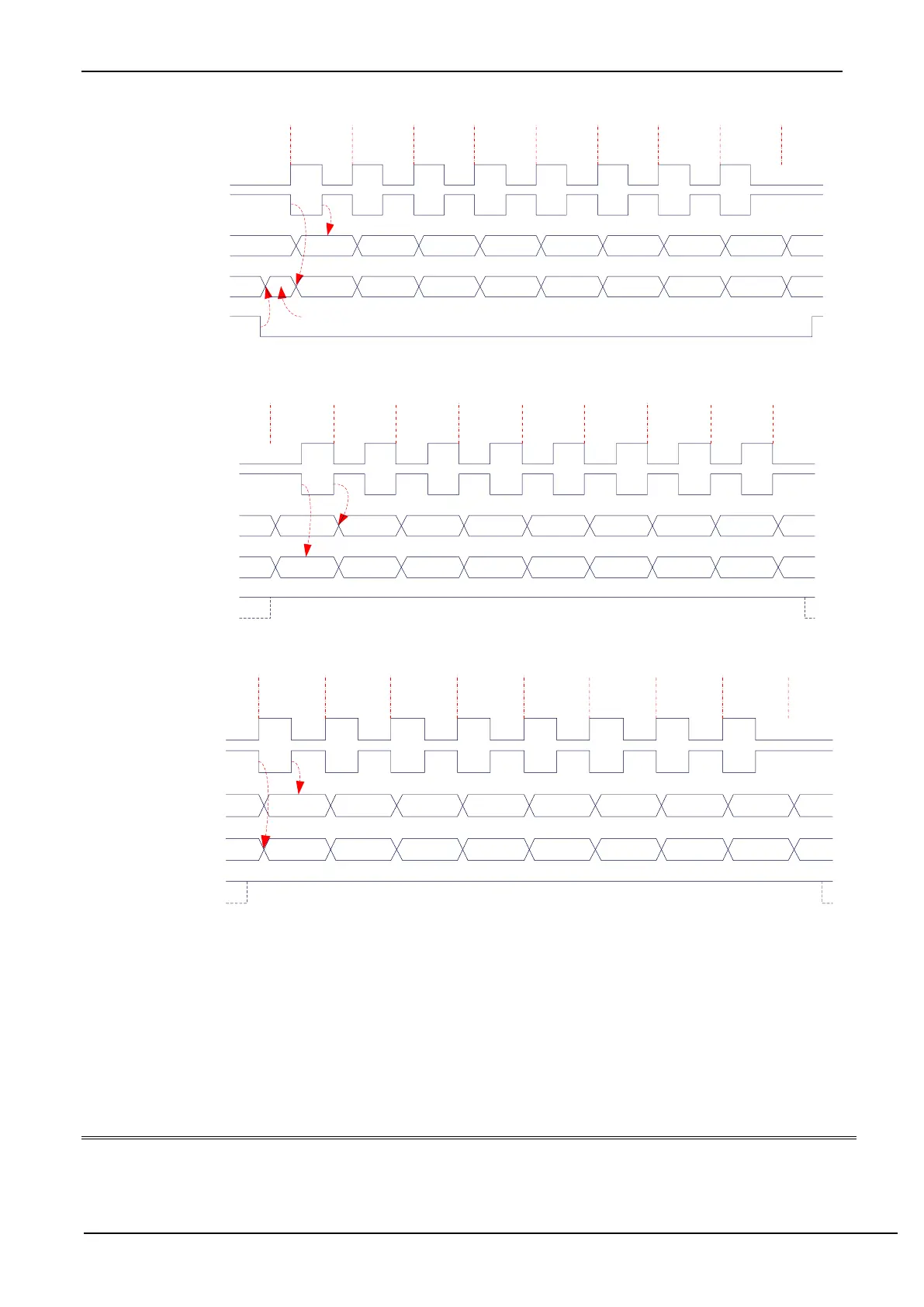

SCLK (CPOL=0)

SCLK (CPOL=1)

MOSI (input)

SPI slave transfer format with CPHA=1

MISO (output)

SS (If SSIG=0)

DORD=0

DORD=1

DORD=0

DORD=1

MSB

LSB MSB

LSB

1

6

2

5

3

4

4

3

5

2

6

1

MSB

LSB MSB

LSB

1

6

2

5

3

4

4

3

5

2

6

1

Sample at the trailing edge

Drive at the leading edge

1 2 3 4 5 6 7 8

Invalid data

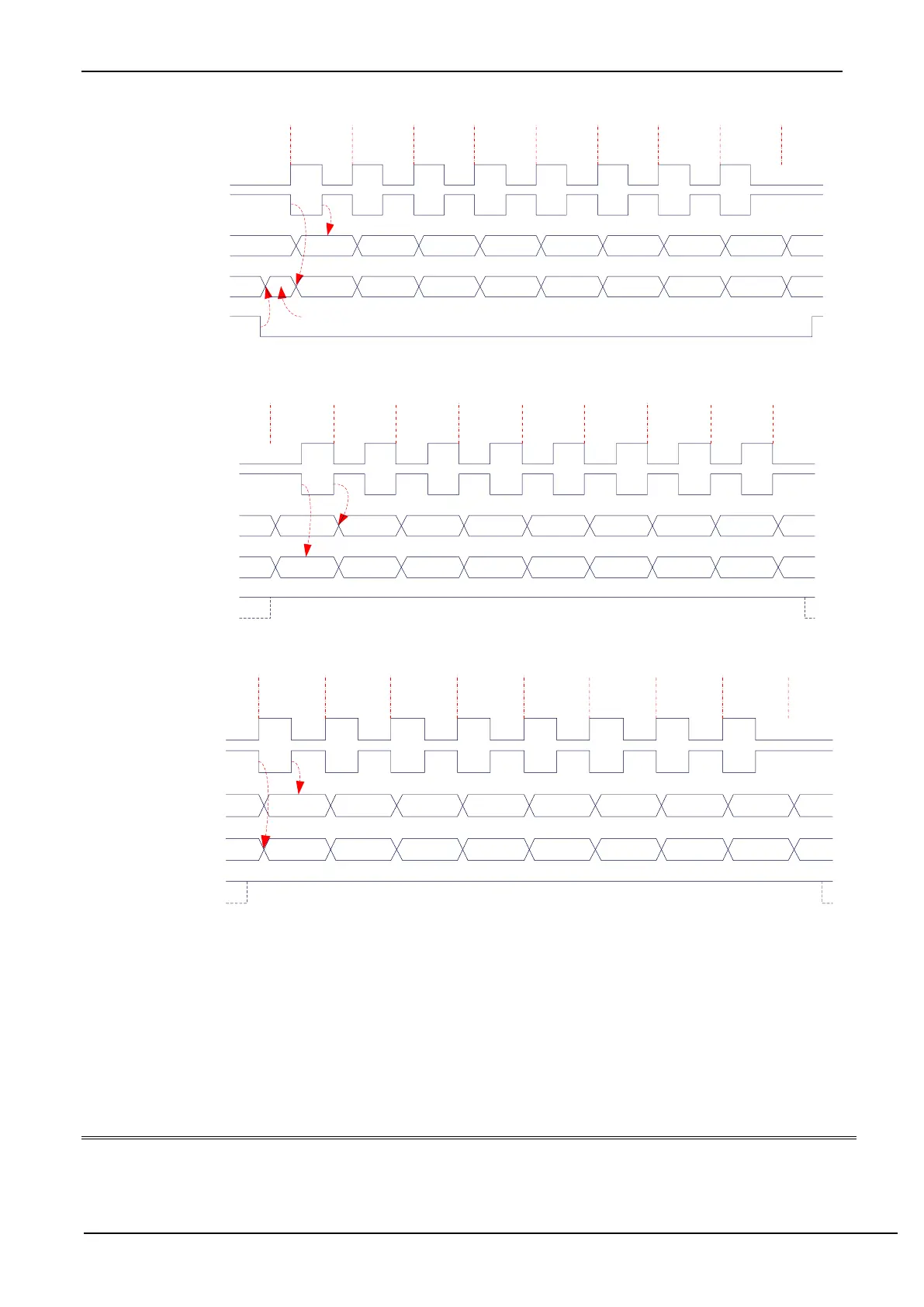

SCLK (CPOL=0)

SCLK (CPOL=1)

MOSI (output)

SPI master transfer format with CPHA=0

MISO (input)

SS (If SSIG=0)

DORD=0

DORD=1

DORD=0

DORD=1

MSB

LSB MSB

LSB

1

6

2

5

3

4

4

3

5

2

6

1

MSB

LSB MSB

LSB

1

6

2

5

3

4

4

3

5

2

6

1

Change data at the trailing edge

Sample at the leading edge

1 2 3 4 5 6 7 8

SCLK (CPOL=0)

SCLK (CPOL=1)

MOSI (output)

SPI master transfer format with CPHA=1

MISO (input)

SS (If SSIG=0)

DORD=0

DORD=1

DORD=0

DORD=1

MSB

LSB MSB

LSB

1

6

2

5

3

4

4

3

5

2

6

1

MSB

LSB MSB

LSB

1

6

2

5

3

4

4

3

5

2

6

1

Sample at the trailing edge

Drive at the leading edge

1 2 3 4 5 6 7 8

20.6 Example Routines

20.6.1 Master Routine of Single Master Single Slave Mode (Interrupt

Mode)

C language code

//Operating frequency for test is 11.0592MHz

Loading...

Loading...