STC8A8K64D4 Series Manual

-

UR2R_DMA configuration

register

UR3T_DMA configuration

register

UR3R_DMA configuration

register

UR4T_DMA configuration

register

UR4R_DMA configuration

register

LCM_DMA configuration register

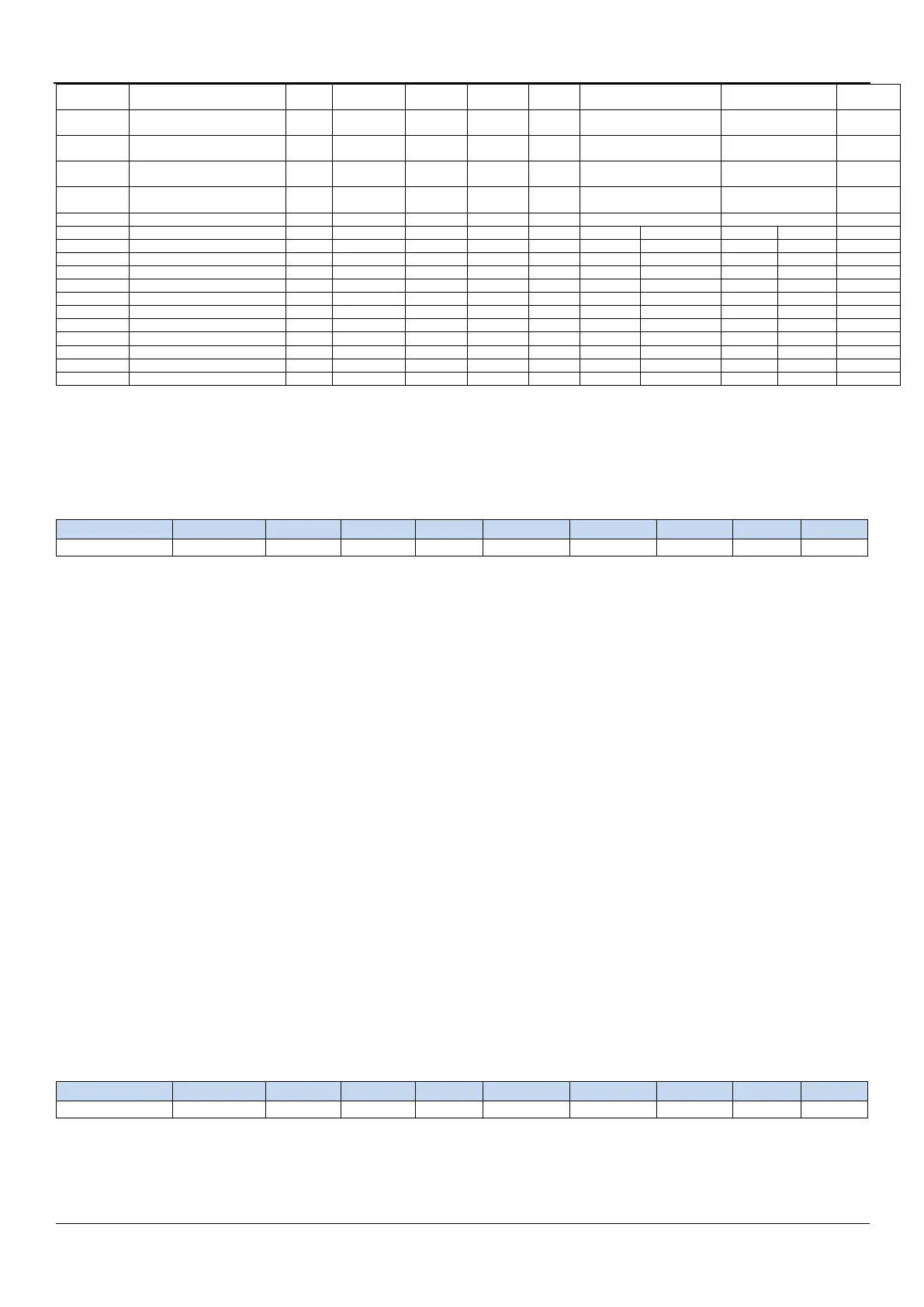

11.4.1 Interrupt Enable Registers (Interrupt Enable bits)

IE (Interrupt Enable Rsgister)

EA: The general or global interrupt enable control bit. The function of EA is to allow interrupts to be multi-level controlled.

That is, every interrupt source is controlled by EA firstly and then by its own interrupt enable control bit.

0: All interrupts are masked.

1: Enable the CPU interrupt, every interrupt source would be individually enabled or disabled by setting or clearing its

enable bit.

ELVD: Low volatge detection interrupt enable bit.

0: disable low voltage detection interrupt.

1: enable Low voltage detection interrupt.

EADC: ADC interrupt enable bit.

0: disable ADC interrupt.

1: enable ADC interrupt.

ES: UART1 interrupt enable bit.

0: disable UART1 interrupt.

1: enable UART1 interrupt.

ET1: Timer 1 interrupt enable bit.

0: disable Timer 1 interrupt.

1: enable Timer 1 interrupt.

EX1: External interrupt 1 enable bit.

0: disable external interrupt 1.

1: enable external interrupt 1.

ET0: Timer 0 interrupt enable bit.

0: disable Timer 0 interrupt.

1: enable Timer 0 interrupt.

EX0: External interrupt 0 enable bit.

0: disable external interrupt 0.

1: enable external interrupt 0.

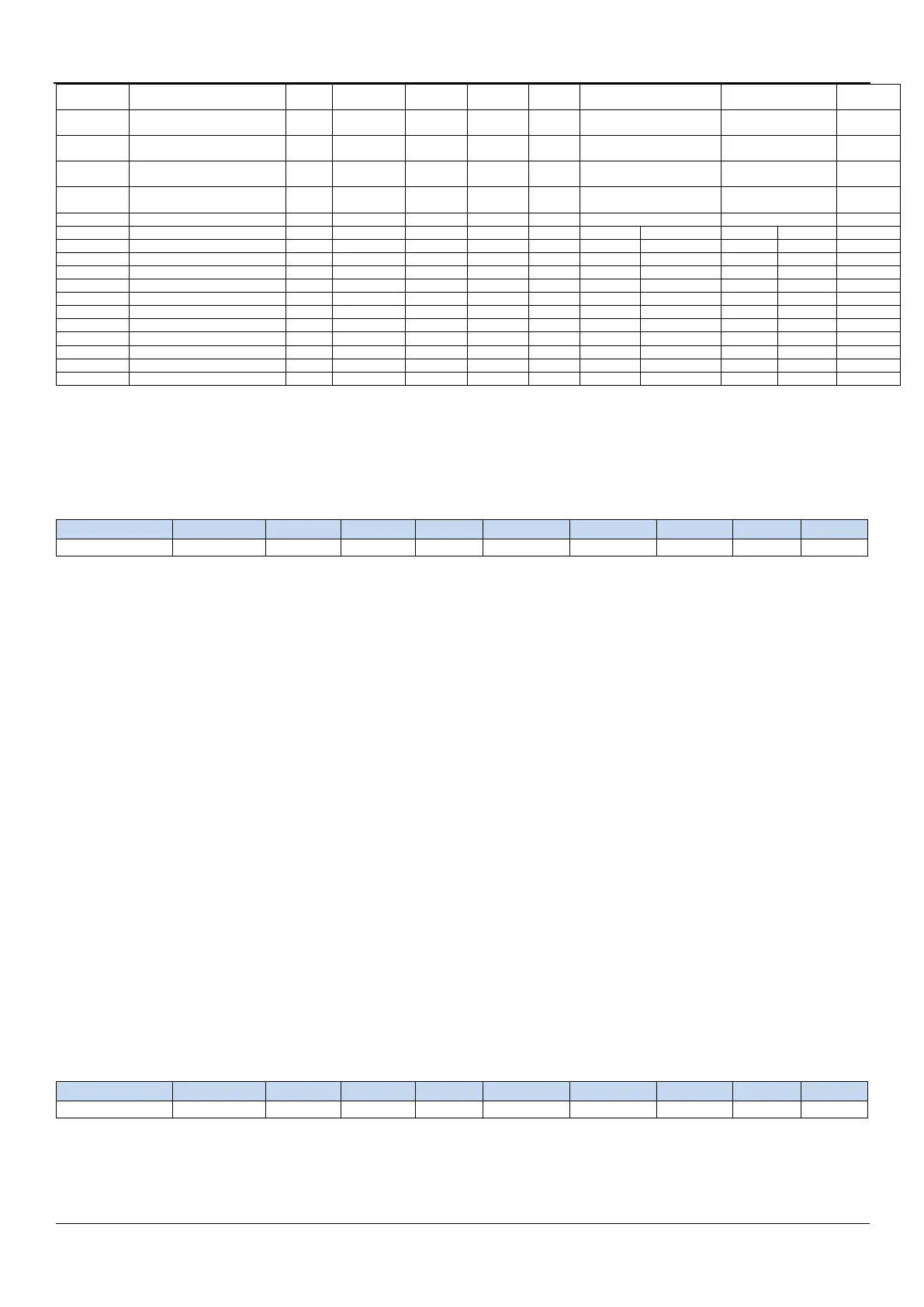

IE2 (Interrupt Enable Rsgister 2)

ET4: Timer 4 interrupt enable bit.

0: disable Timer 4 interrupt.

1: enable Timer 4 interrupt.

ET3: Timer 3 interrupt enable bit.

0: disable Timer 3 interrupt.

Loading...

Loading...