STC8A8K64D4 Series Manual

25 MDU16 Hardware 16-bit Multiplier and Divider

A 16-bit hardware multiply / divide unit MDU16 is integrated in some microcontrollers of the STC8A8K64D4 series.

The following data operations are supported:

➢ Data standardization (need 3-20 clocks of computing time)

➢ Logic left shift (need 3~18 clocks of operation time)

➢ Logic shift right (need 3~18 clocks of operation time)

➢ 16 bits multiplied by 16 bits (it takes 10 clocks of operation time)

➢ 16 bits divided by 16 bits (need 9 clocks of operation time)

➢ 32 bits divided by 16 bits (requires 17 clocks of operation time)

All operations are based on unsigned integer data types.

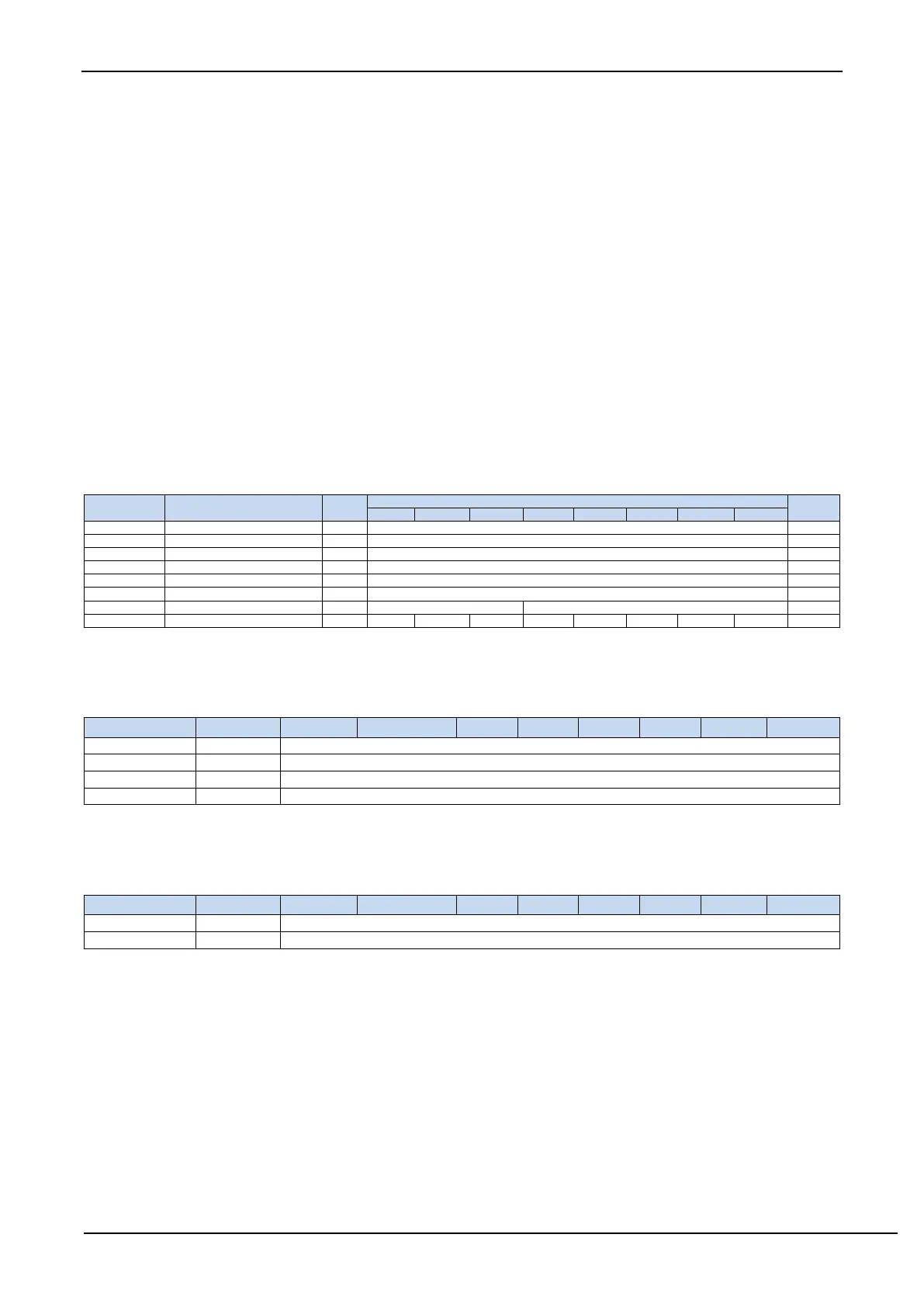

25.1 Registers Related to MDU16

MDU Mode Control Register

MDU Operation Control Register

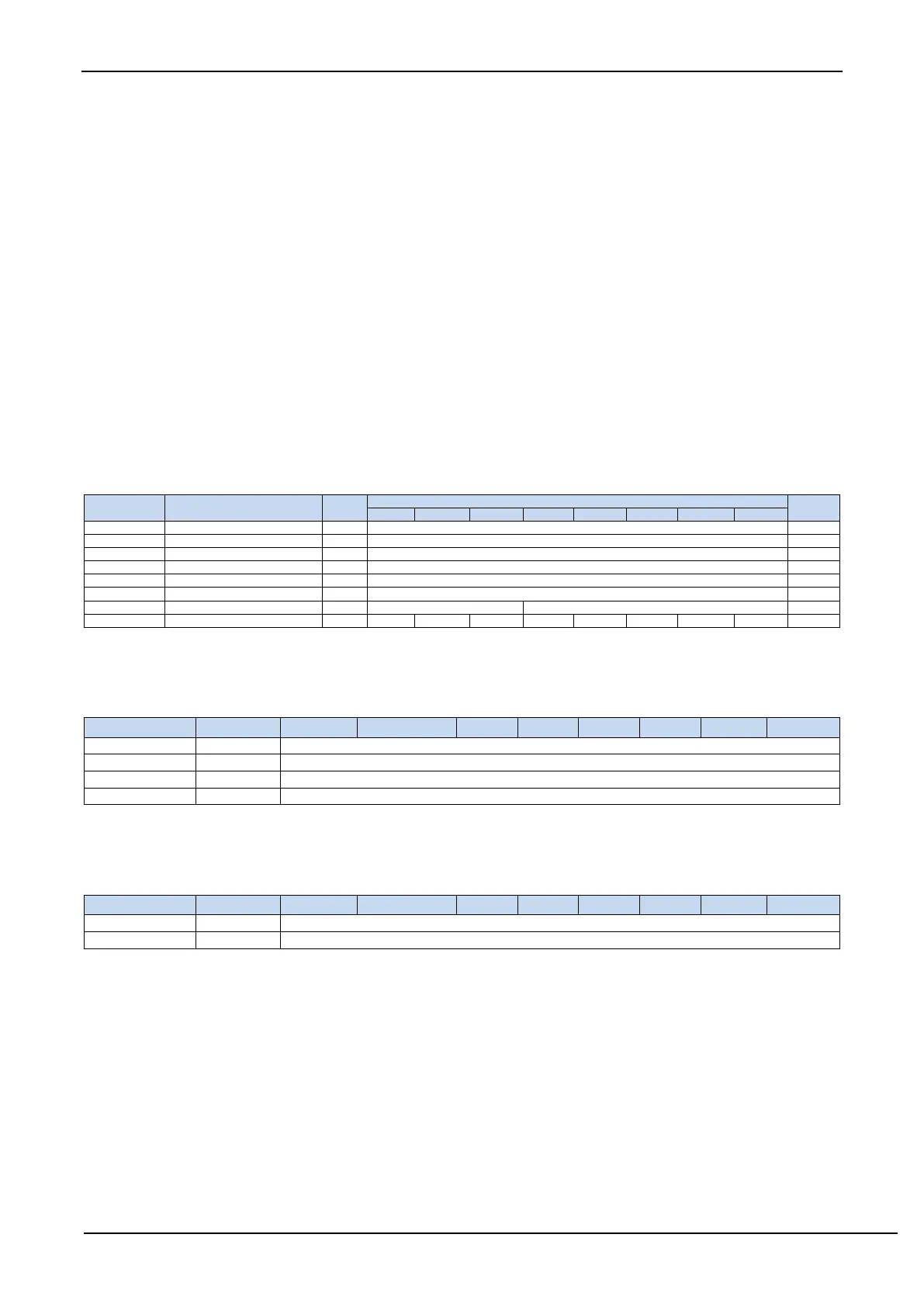

25.1.1 Operand 1 Data Registers (MD0~MD3)

25.1.2 Operand 2 Data Registers (MD4~MD5)

32-bit division by 16-bit division:

Dividend: {MD3,MD2,MD1,MD0}

Divisor: {MD5,MD4}

Quotient: {MD3,MD2,MD1,MD0}

Remainder: {MD5,MD4}

16-bit division by 16-bit division:

Dividend: {MD1,MD0}

Divisor: {MD5,MD4}

Quotient: {MD1,MD0}

Remainder: {MD5,MD4}

16-bit multiplication by 16-bit multiplication:

Multiplicand: {MD1,MD0}

Loading...

Loading...