21 I

2

C Bus

An I

2

C serial bus controller is integrated in the STC8A8K64D4 series of microcontrollers. I

2

C is a high-speed

synchronous communication bus, which uses SCL (clock line) and SDA (data line) to carry out two-wire synchronous

communication. For the pin allocation of SCL and SDA, STC8A8K64D4 series of microcontrollers provide pin switch

mode that can switch SCL and SDA to different I/O pins. Therefor, it is convenience to use a set of I

2

C as multiple sets

of I

2

C buses through time sharing.

Compared with the standard I

2

C protocol, the following two mechanisms are ignored:

⚫ No arbitration will be performed after the start signal (START) is sent.

⚫ No timeout detection when the clock signal (SCL) stays at low level.

The I

2

C bus of the STC8A8K64D4 series of microcontrollers offer two modes of operation: master mode (SCL is

the output port, which is used to transmit synchronous clock signal) and slave mode (SCL is the input port, which is

used to receive the synchronous clock signal).

STC innovation: When the I

2

C serial bus controller of STC works in slave mode, the falling edge signal of SDA

pin can wake up the MCU which is in power-down mode. (Note: Due to the fast I

2

C transmission speed, the first packet

of data after the MCU wakes up is generally incorrect.)

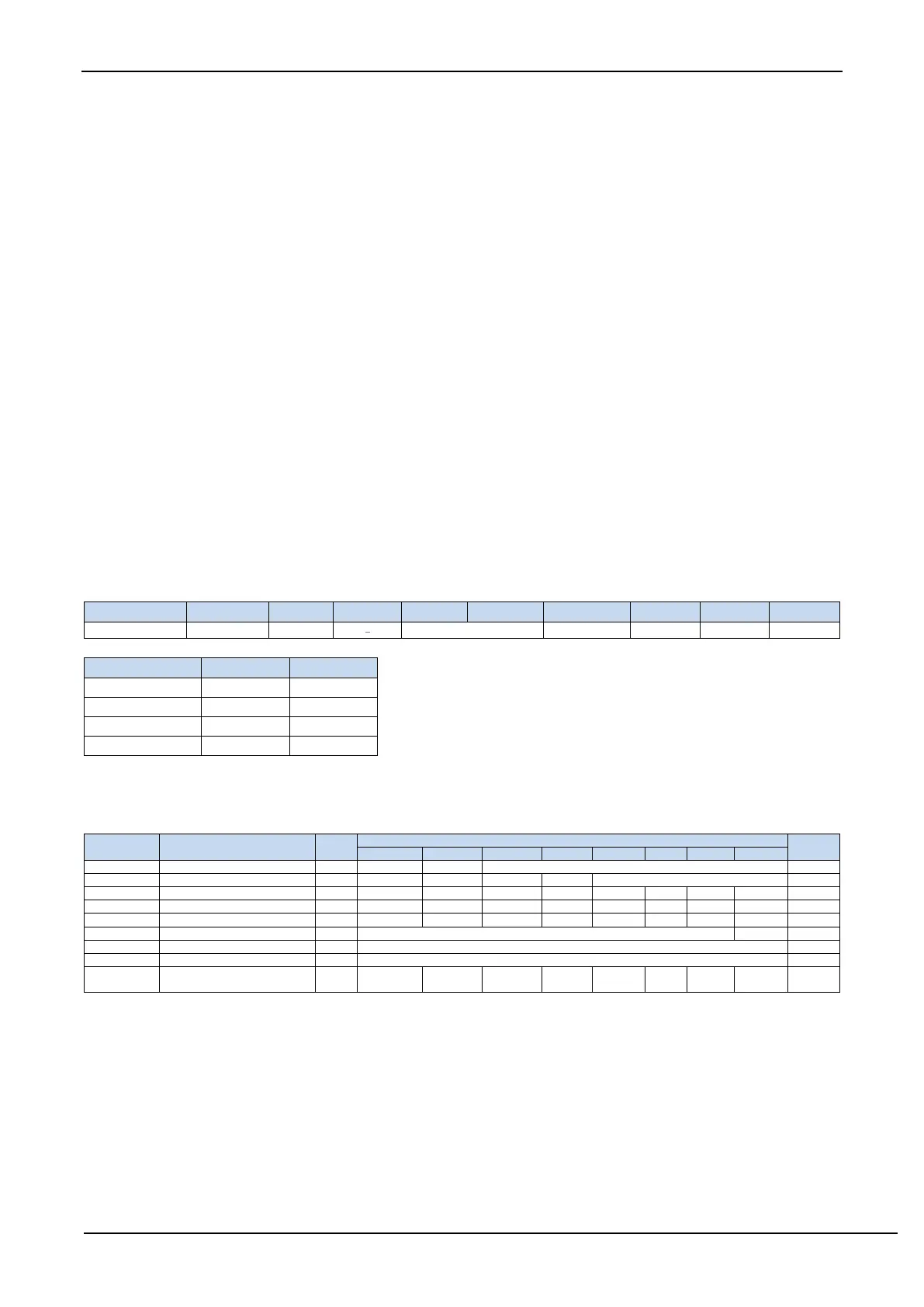

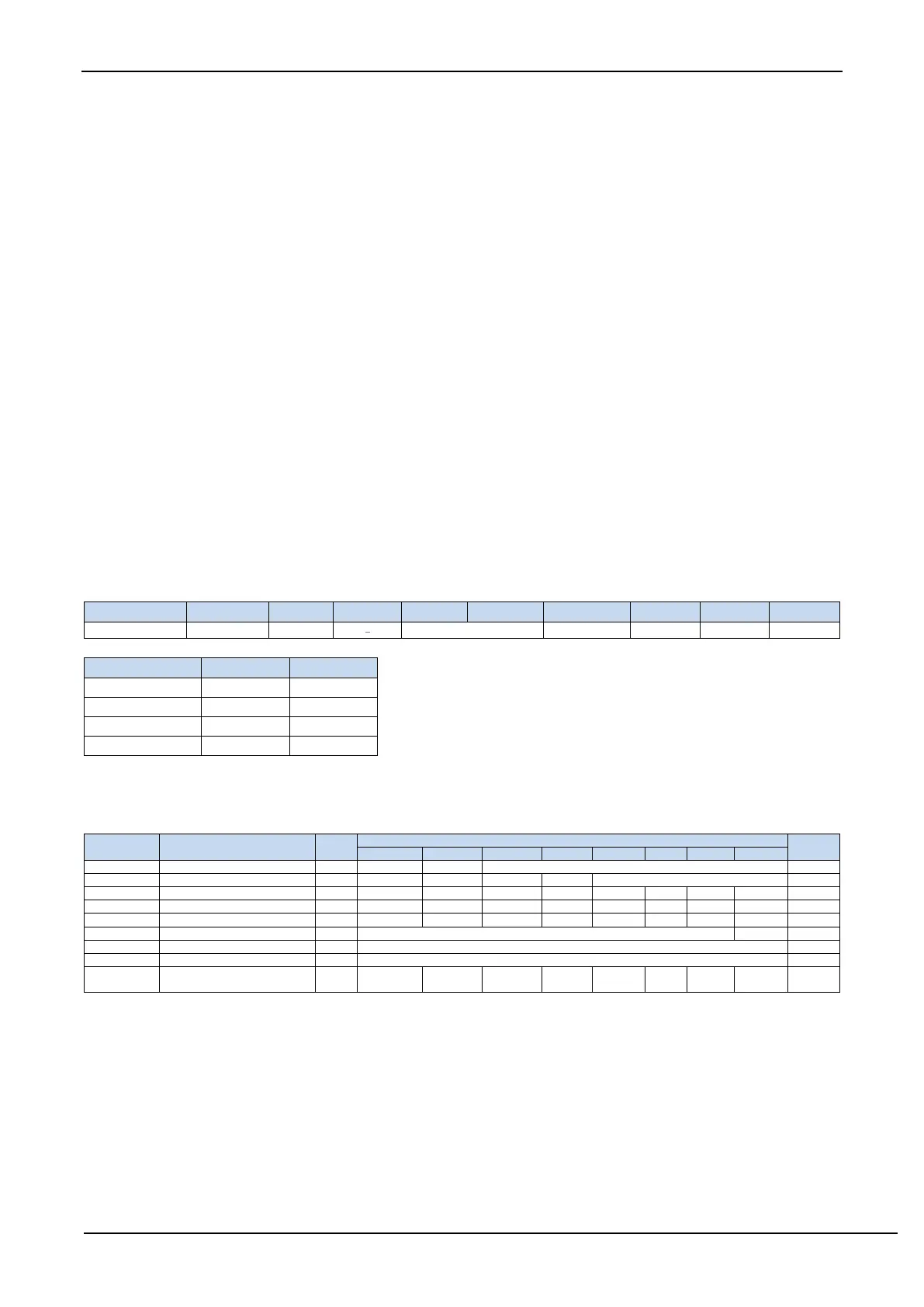

21.1 I2C function pin switch

Loading...

Loading...