STC8A8K64D4 Series Manual

23.9 Data exchange between LCM and memory (LCM_DMA)

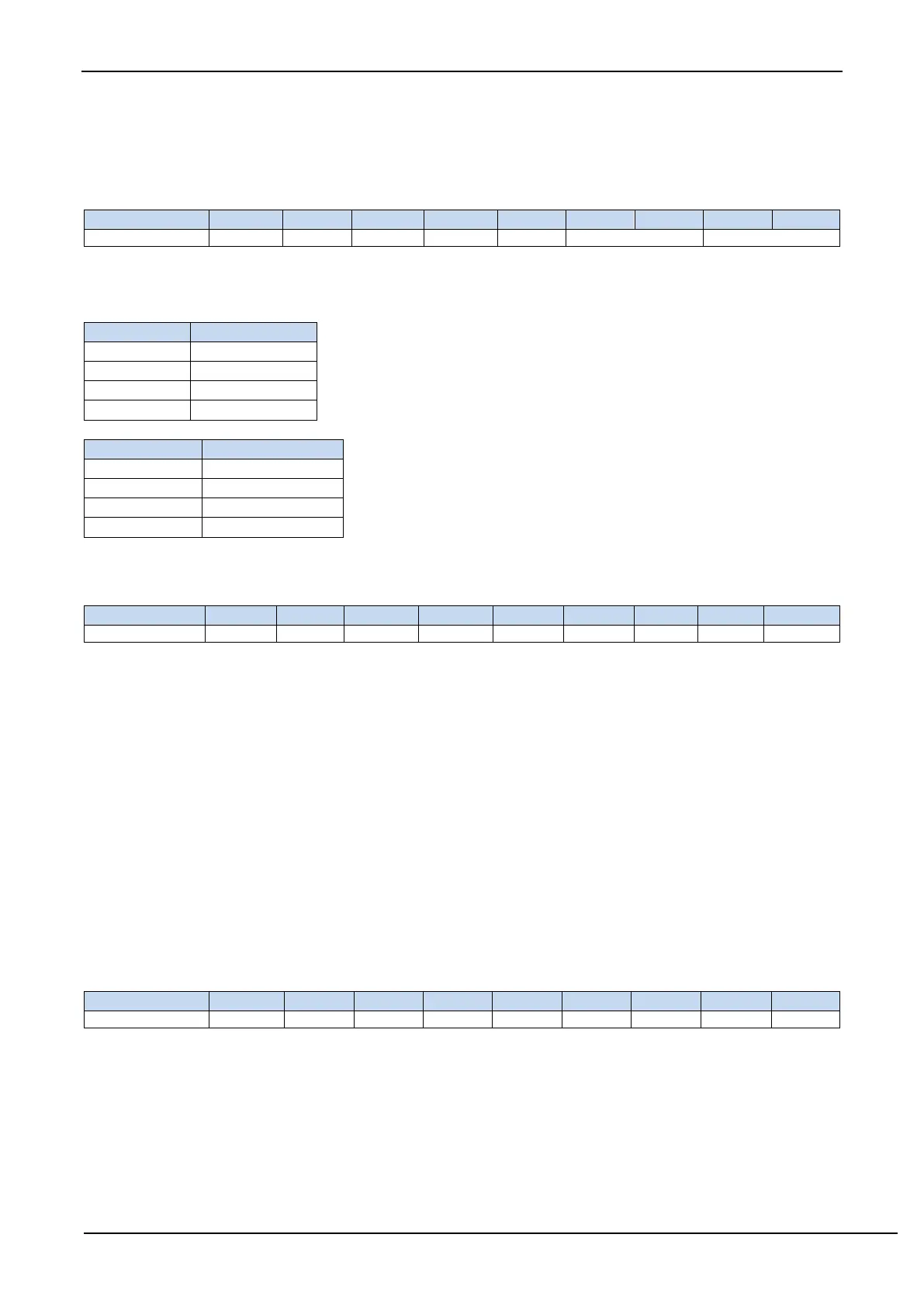

23.9.1 LCM_DMA Configuration Register (DMA_LCM_CFG)

LCMIE: LCM_DMA interrupt enable control bit

0: Disable LCM_DMA interrupt

1: Enable LCM_DMA interrupt

LCMIP [1:0]: LCM_DMA interrupt priority control bits

LCMPTY[1:0]: LCM_DMA Data bus access priority control bits

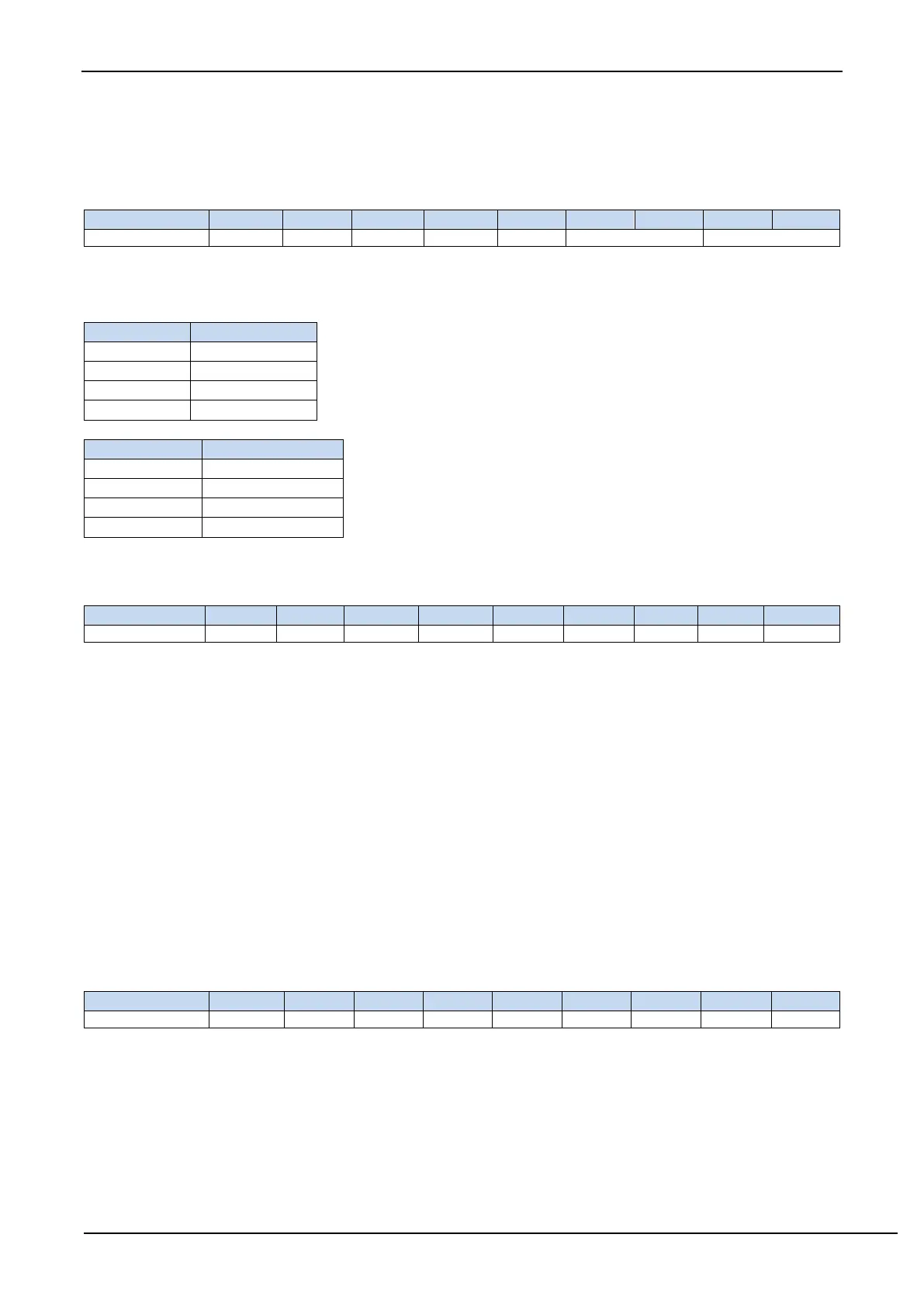

23.9.2 LCM_DMA Control Register (DMA_LCM_CR)

ENLCM: LCM_DMA function enable control bit

0: Disable LCM_DMA function

1: Enable LCM_DMA function

TRIGWC: LCM_DMA send command mode trigger control bit

0: Write 0 is invalid

1: Write 1 to start LCM_DMA send command mode operation

TRIGWD: LCM_DMA send data mode trigger control bit

0: Write 0 is invalid

1: Write 1 to start LCM_DMA send data mode operation

TRIGRC: LCM_DMA read command mode trigger control bit

0: Write 0 is invalid

1: Write 1 to start LCM_DMA read command mode operation

TRIGRD: LCM_DMA read data mode trigger control bit

0: Write 0 is invalid

1: Write 1 to start LCM_DMA read data mode operation

23.9.3 LCM_DMA Status Register (DMA_LCM_STA)

LCMIF: LCM_DMA interrupt request flag bit. After the LCM_DMA data exchange is completed, the hardware

automatically sets LCMIF to 1. If the LCM_DMA interrupt is enabled, the interrupt service routine is entered. The

flag bit needs to be cleared by software

TXOVW: LCM_DMA data coverage flag. When LCM_DMA is in the process of data transmission, and LCMIF writes

the LCMIFDATL and LCMIDDATH registers, the data transmission will fail. At this time, the hardware will

automatically set TXOVW to 1. The flag bit needs to be cleared by software

Loading...

Loading...