STC8A8K64D4 Series Manual

-

be an external pull-up resistor in this configuration when the port outputs a logic high, typically the port pin is externally

connected to VCC through a resistor. An open-drain I/O port pin can read the external state if the external pull-up resistor is

connected, and the open-drain mode I/O port pin can be used as input mode. The pull-down structure in this way is the same

as quasi-bidirectional mode.

The open drain port has a Schmitt trigger input and an interference suppression circuit.

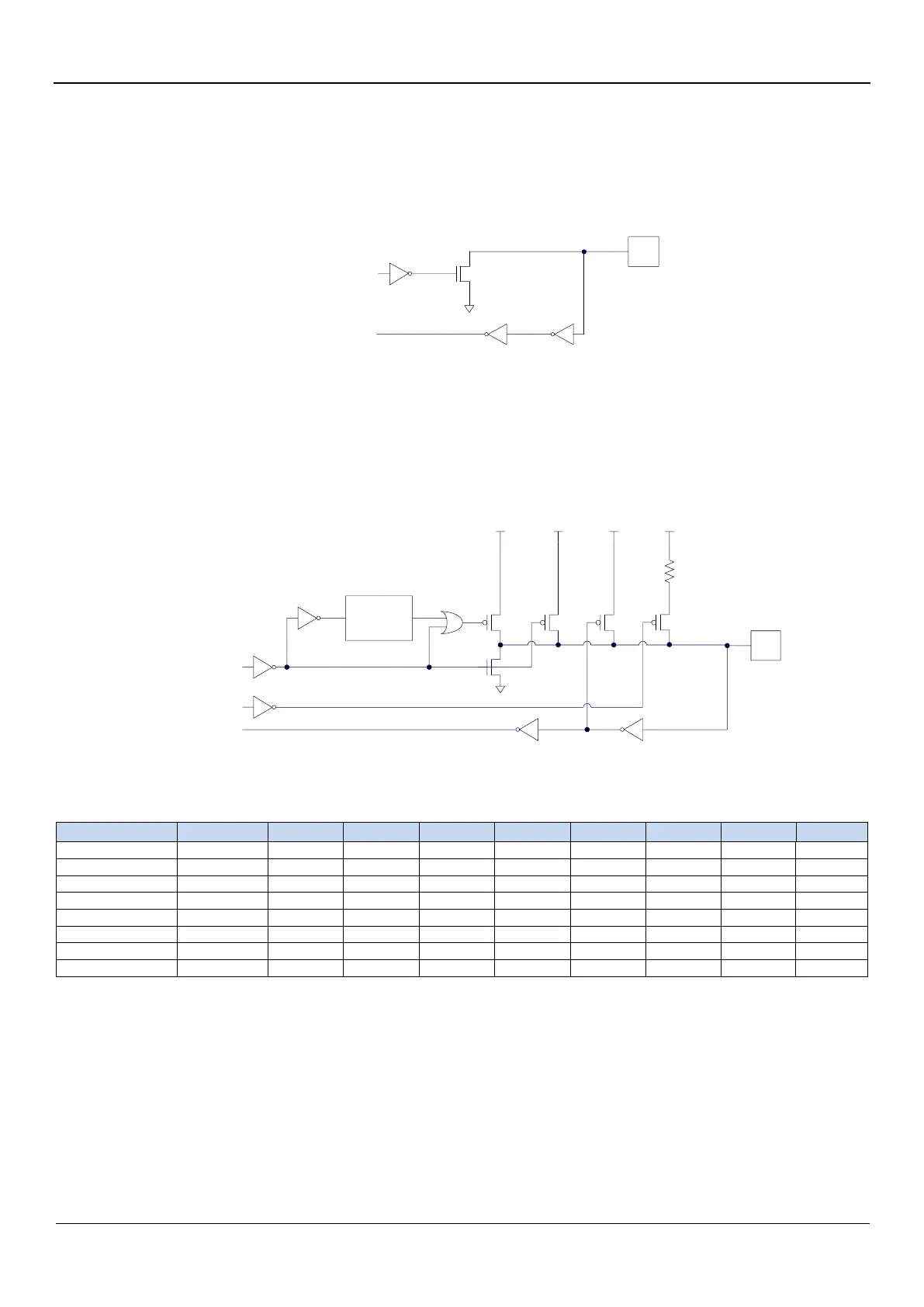

The structure of open drain port configuration is shown below:

Port latch data

Input data

interference suppression

Port

Pin

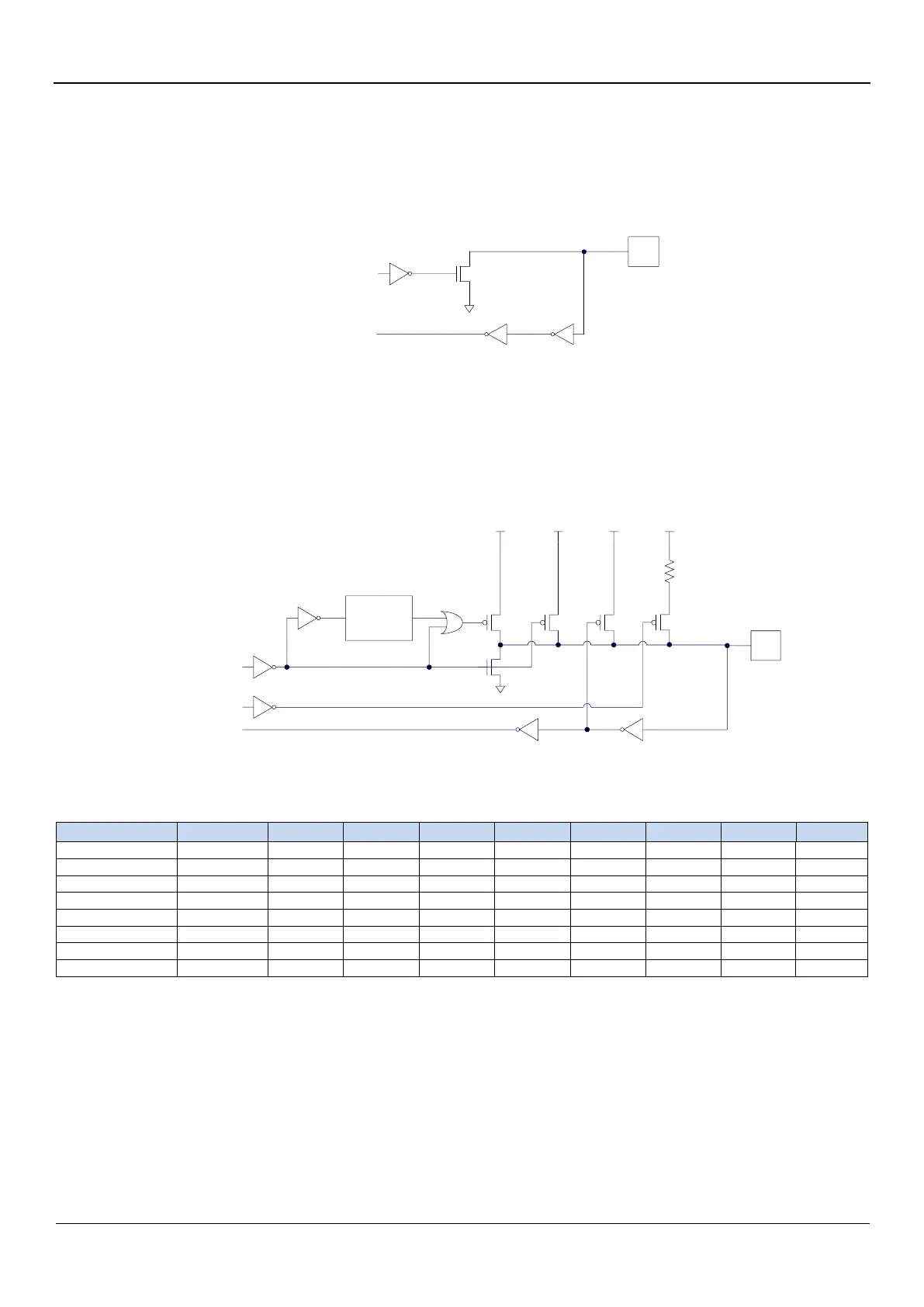

9.3.5 4.1K Pull-up Resistor

A pull-up resistor of approximately 4.1K can be enabled internally in all I/O ports of the STC8 series (due to

manufacturing errors, the range of the pull-up resistor may be 3K to 5K).

Port latch data

2 clocks

delay

VCCVCC VCC

Input Data

Strong

Very

weak

Weak

Port

Pin

interference suppression

VCC

4.1K Pull-up resistor

PxPU control bit

Pull-up Resistor Control Registers

Internal 4.1K pull-up resistor control bit (Note: The pull-up resistors on the P3.0 and P3.1 ports may be slightly smaller)

0: Disable 4.1K pull-up resistor inside the port

1: Enable 4.1K pull-up resistor inside the port

9.3.6 How to set the external output speed of the I/O port

When users need the I/O port to output a faster frequency, they can increase the I/O port drive current and increase the I/O port level

conversion speed to increase the I/O port output speed.

Setting the PxSR register can be used to control the I/O port level conversion speed. When it is set to 0, the corresponding I/O port is fast

flipping, and when it is set to 1, it is slow flipping.

Loading...

Loading...