STC8A8K64D4 Series Manual

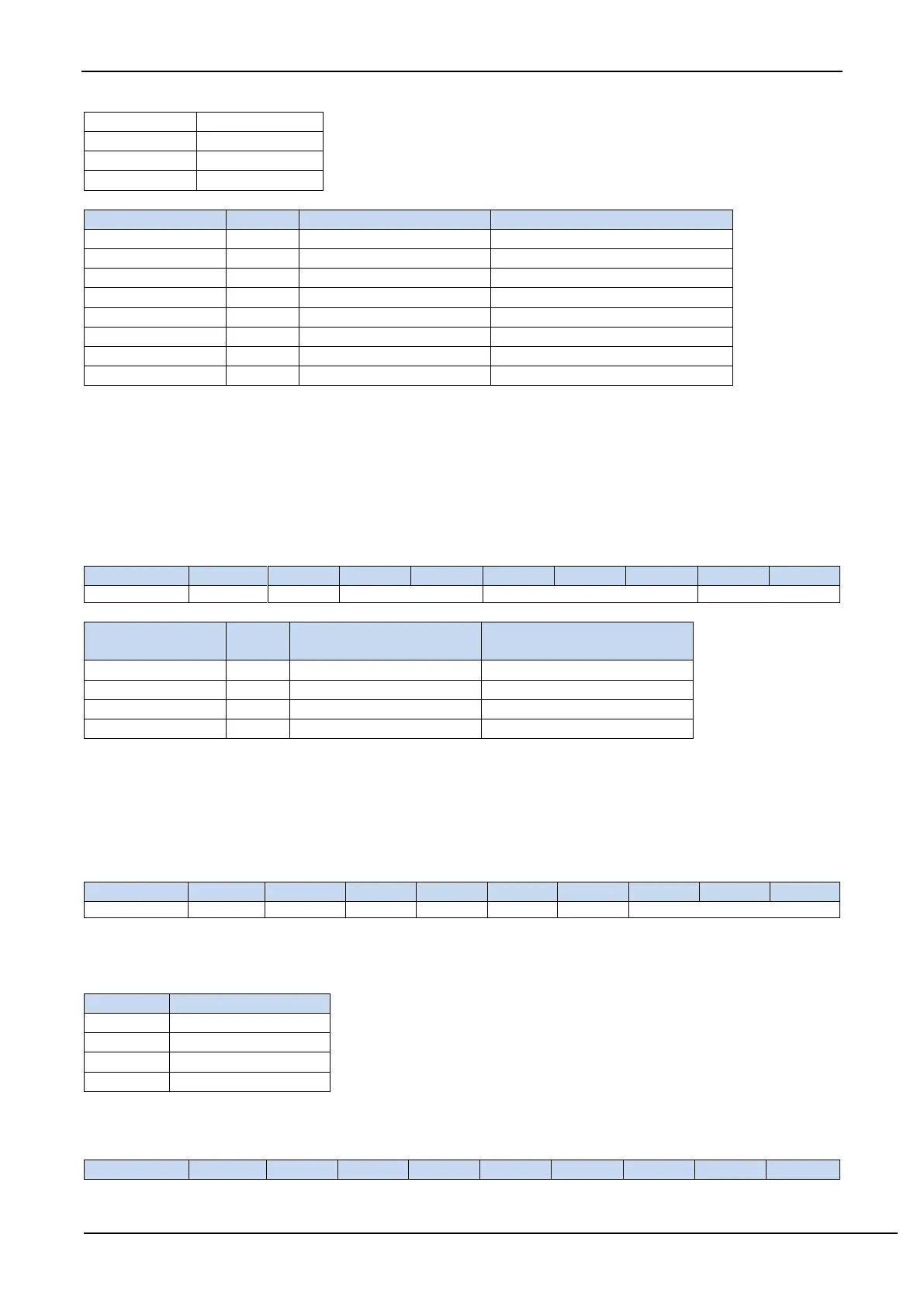

LCMIFDPS[1:0]: LCM interface data pin selection bit

D16_D8: LCM interface data width control bit

0: 8-bit data width

1: 16-bit data width

M68_I80: LCM interface mode selection bit

0: I8080 mode

1: M6800 mode

22.2.2 LCM Interface Configuration Register 2 (LCMIFCFG2)

LCMIFCPS[1:0]: LCM interface control pin selection bit

RD signal of I8080

E signal of M6800

WR signal of I8080

RW signal of M6800

SETUPT[2:0]: Data setup time control bit for LCM interface communication (see timing diagrams in subsequent

chapters for details)

HOLDT[1:0]: Data hold time control bit for LCM interface communication (see the timing diagram in the subsequent

chapters for details)

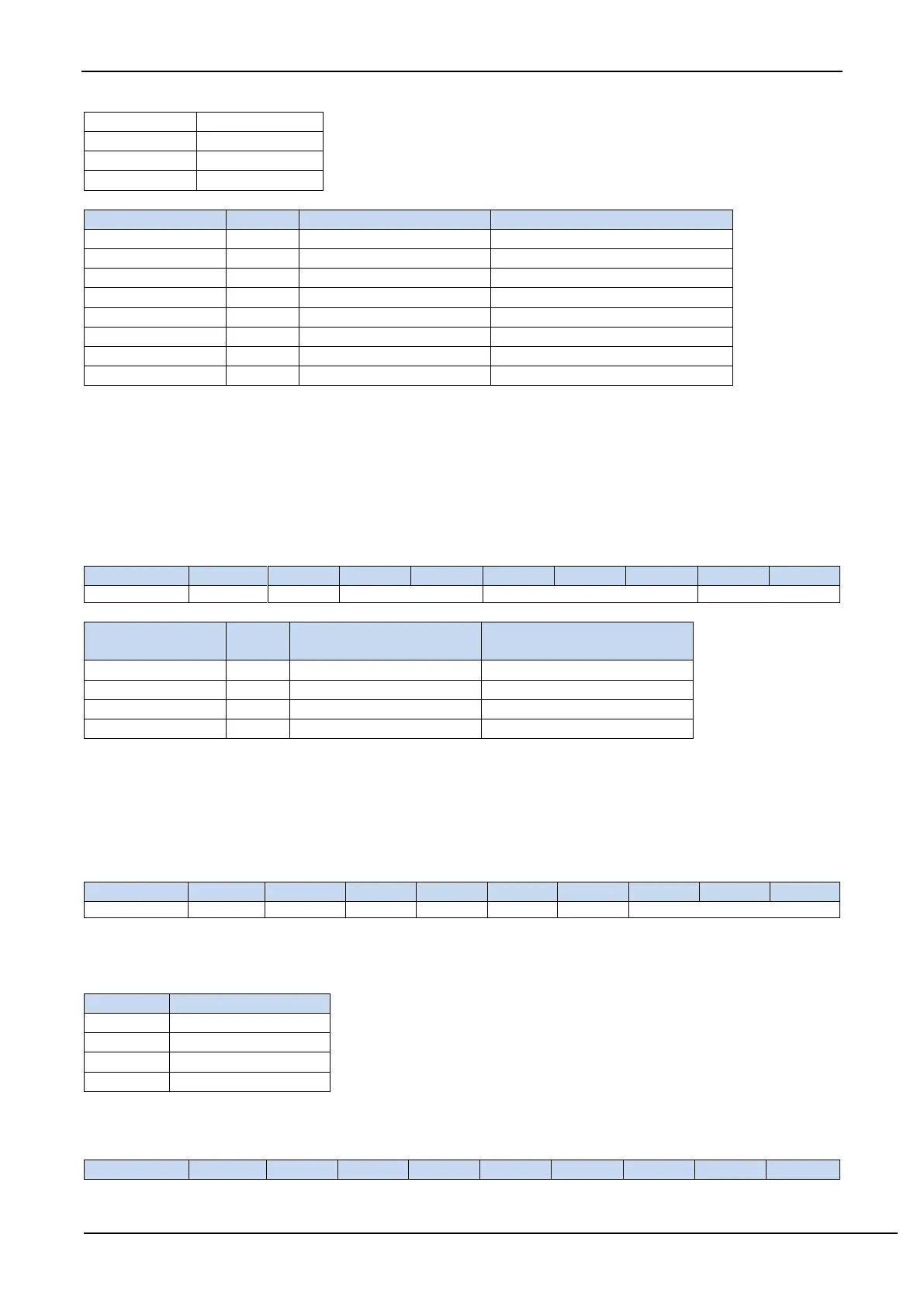

22.2.3 LCM Interface Control Register (LCMIFCR)

ELCMIF: LCM interface enable control bit

0: Disable LCM interface function

1: Enable LCM interface function

CMD[2:0]: LCM interface trigger command

22.2.4 LCM Interface Status Register (LCMIFSTA)

Loading...

Loading...