STC8A8K64D4 Series Manual

14.5 UART3

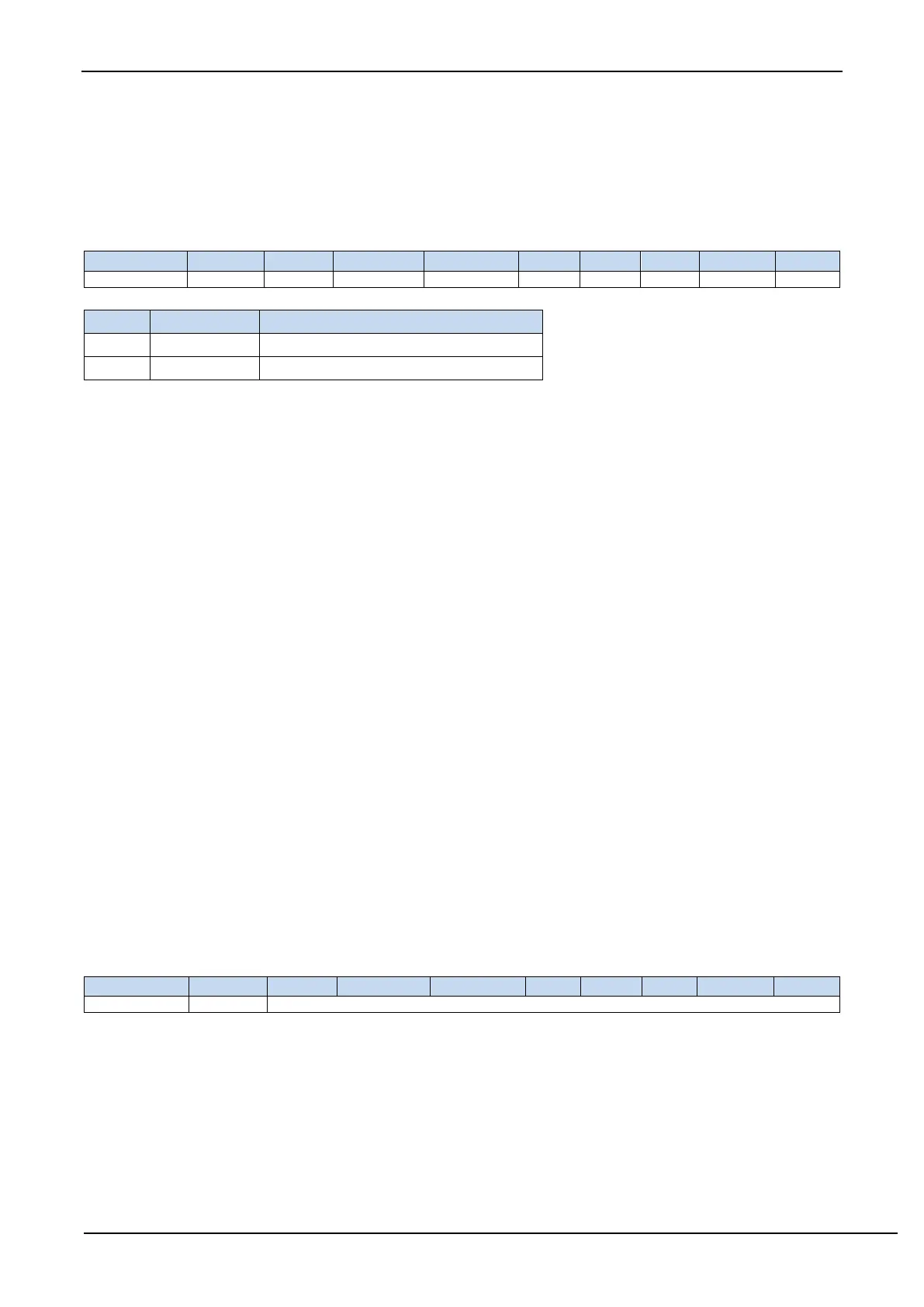

14.5.1 UART3 control register

S3SM0: UART3 mode select bit.

8-bit UART, whose baud-rate is variable

9-bit UART, whose baud-rate is variable

S3ST3: UART3 baud rate generator select bit.

0: Select T2 as the baud-rate generator of UART3.

1: Select T3 as the baud-rate generator of UART3.

S3SM2: UART3 multi-machine communication control bit. In mode 1, if the S3SM2 bit is 1 and the S3REN bit is 1,

the receiver is in the address frame filter state. In this case, the received 9th bit (S3RB8) can be used to filter the

address frame. If S3RB8 = 1, the frame is the address frame, address information can enter S3BUF, S3RI

becomes 1, and then the address is compared with the slave address in the interrupt service routine. If S3RB8 =

0, it indicates that the frame is not an address frame and should be discarded and keep S3RI = 0. In mode 1, if

the S3SM2 bit is 0 and the S3REN bit is 1, the receiver is in the address frame filter disabled state. Regardless

of the received S3RB8 is 0 or 1, the information received can enter into the S3BUF, and make S3RI = 1. Here,

S3RB8 is usually used as parity check bit. Mode 0 is non-multi-machine communication mode, where S3SM2

should be 0.

S3REN: Receive enable control bit.

0: disable UART3 receive data.

1: enable UART3 receive data.

S3TB8: S3TB8 is the 9

th

bit of datum to be sent when UART3 is in mode 1, which is usually used as a parity check bit

or an address frame / data frame flag. It can be set or cleared by software as required. In mode 0, this bit is not

used.

S3RB8: S3RB8 is the 9

th

bit of datum recieved when UART3 is in mode 1, which is usually used as a parity check bit

or an address frame / data frame flag. It can be set or cleared by software as required. In mode 0, this bit is not

used.

S3TI: Transmit interrupt request flag of UART3. S3TI is set by the hardware automatically at the beginning of the stop

bit transmittion and requests interrupt to the CPU. S3TI must be cleared by software after the interrupt is

responded.

S3RI: Receive interrupt request flag of UART3. S3RI is set by hardware automatically at the middle of stop bit the

serial port received, and requests interrupt to the CPU. After the interrupt is responded, S3RI must be cleared

by software.

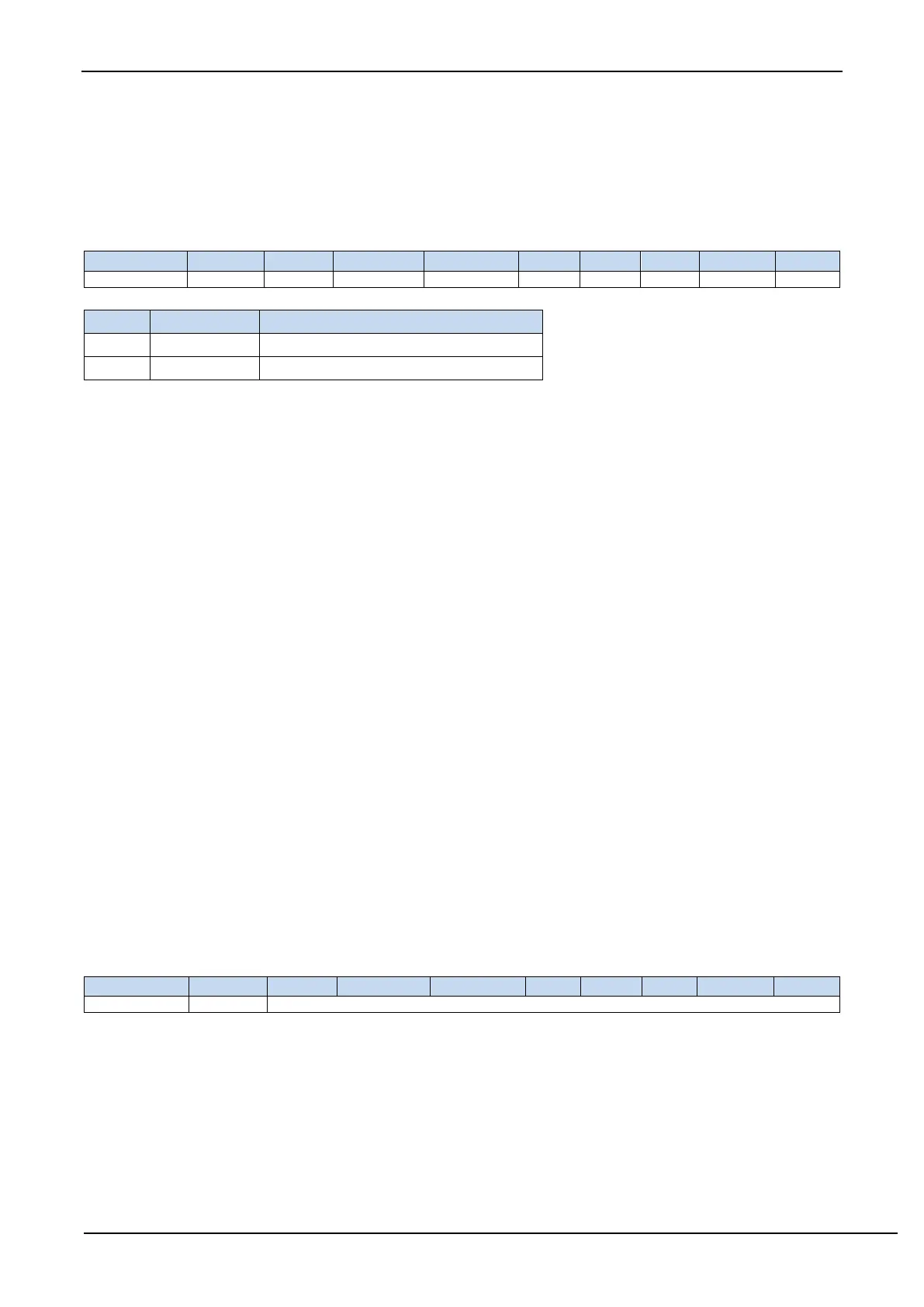

14.5.2 UART3 data register

S3BUF: It is used as the buffer in transmission and receiving for UART3. S3BUF is actually two buffers, reading buffer

and writing buffer. Two operations correspond to two different registers, one is write-only register (writing

buffer), the other is read-only register (reading buffer). The CPU reads serial receive buffer when reads S3BUF,

and writes to the S3BUF will trigger the serial port to start sending data.

14.5.3 UART3 Mode 0

UART3 mode 0 is a 8-bit UART mode with variable baud rate, where a frame of data consists 10 bits: 1 start bit,

8 data bits (LSB first) and 1 stop bit. The baud rate is variable, which can be set by the software as needed. TxD3 is the

Loading...

Loading...