STC8A8K64D4 Series Manual

-

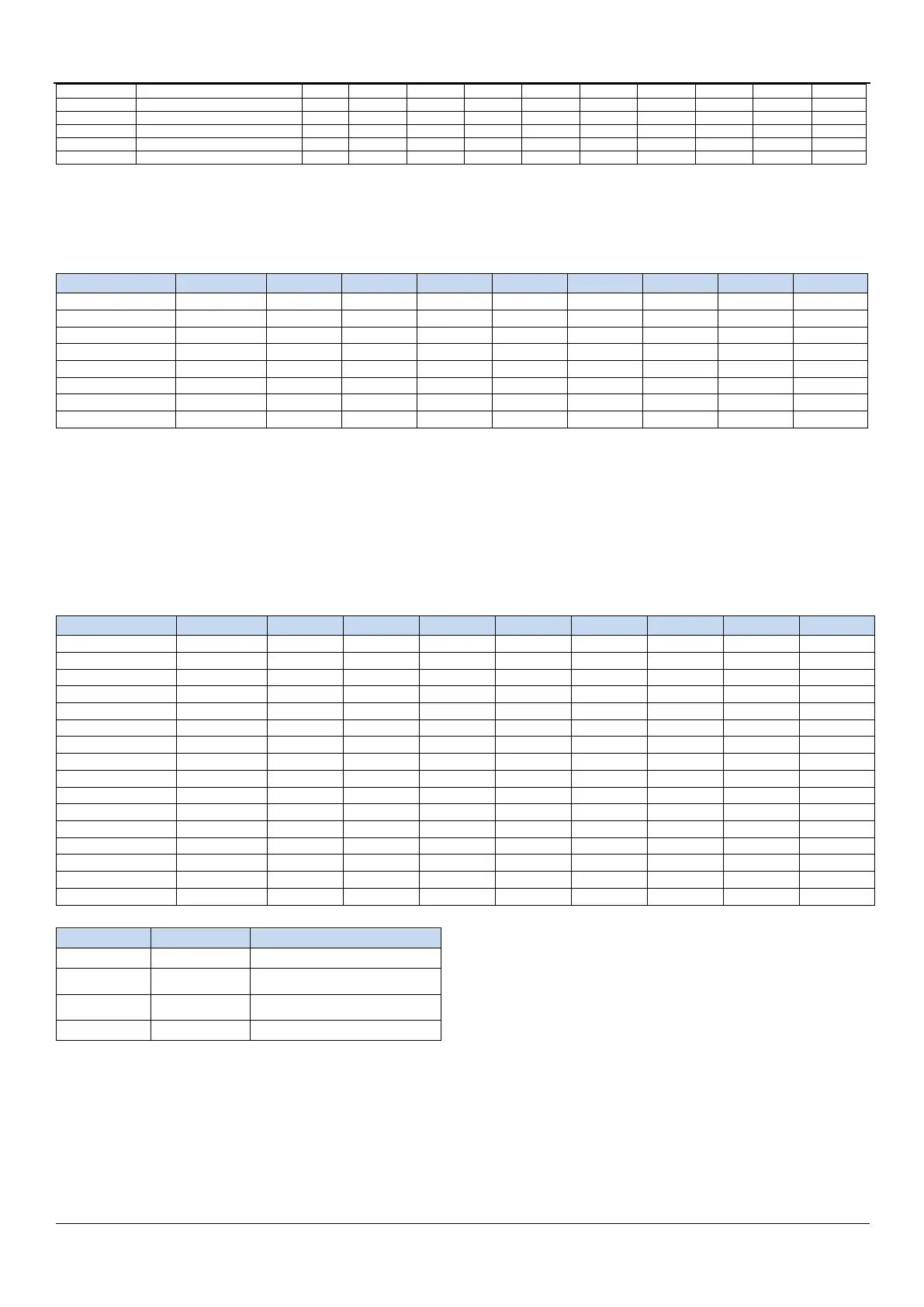

P2 Input Enable Control Register

P3 Input Enable Control Register

P4 Input Enable Control Register

P5 Input Enable Control Register

P6 Input Enable Control Register

P7 Input Enable Control Register

9.1.1 Port Data Register (Px)

Read and write port status

Write 0: Output low to port buffer.

Write 1: Output high to port buffer.

Read: Read the level on the port pin directly.

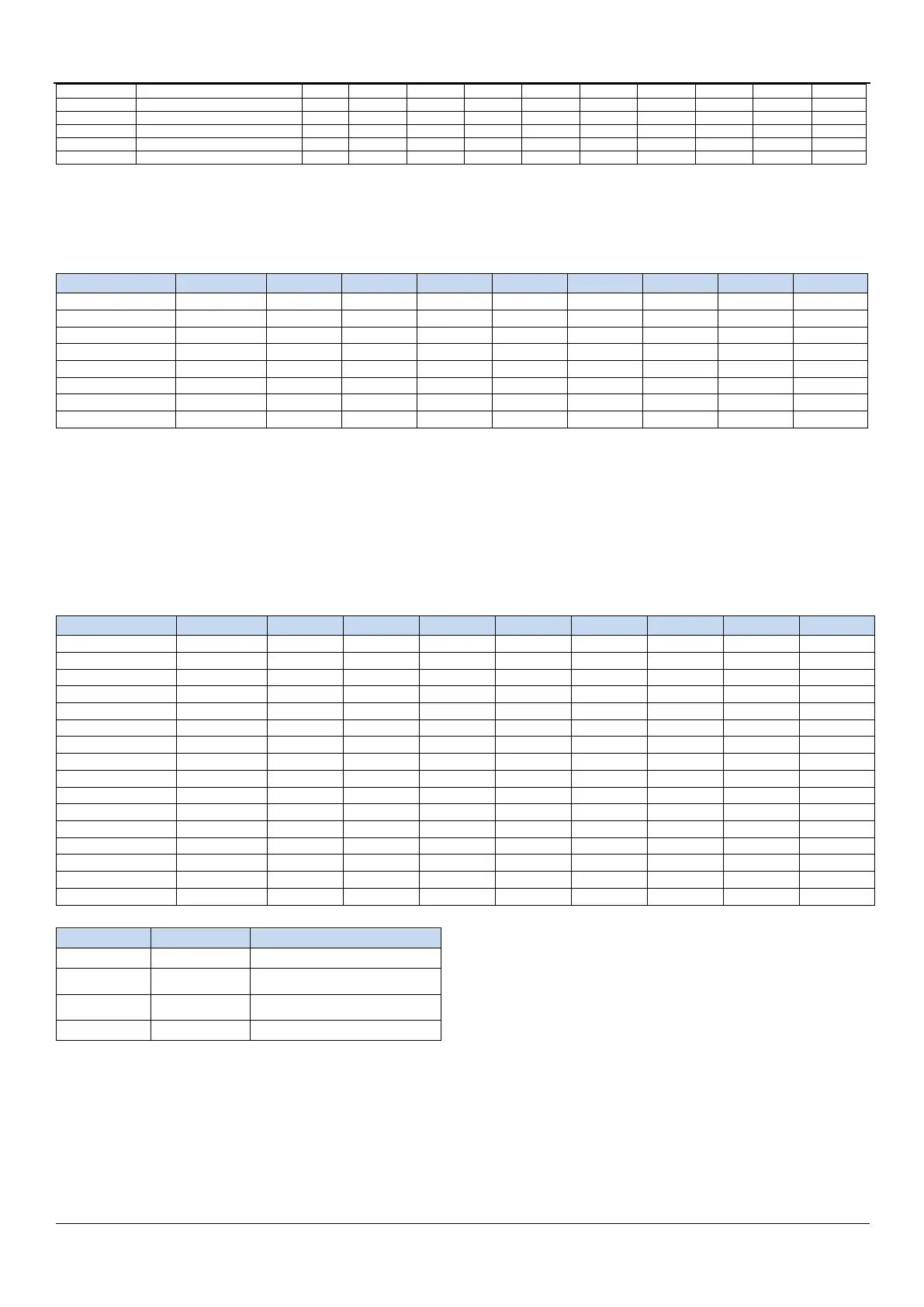

9.1.2 Ports Mode Registers (PxM0, PxM1)

Configure the mode of the ports as shown below.

high-impedance input mode

Note: When an I/O port is selected as the ADC input channel, the PxM0/PxM1 register must be set to set the I/O port

mode to input mode. In addition, if the ADC channel still needs to be enabled after the MCU enters the power-down

mode/clock stop mode, you need to set the PxIE register to close the digital input to ensure that there will be no

additional power consumption.

Loading...

Loading...