STC8A8K64D4 Series Manual

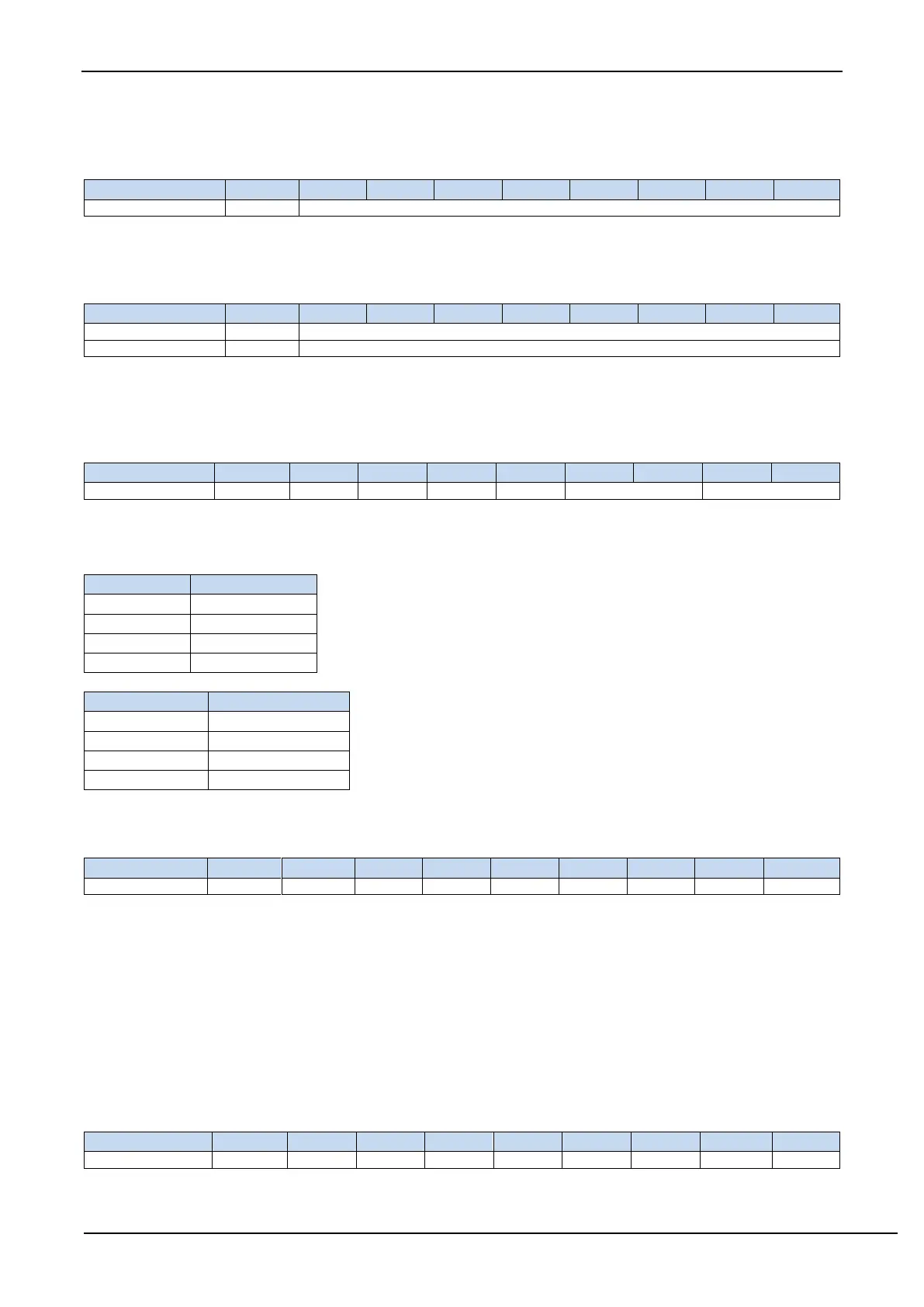

23.8.5 UR4T_DMA transfer complete byte register (DMA_UR4T_DONE)

DMA_UR4T_DONE: The number of bytes that have been sent so far.

23.8.6 UR4T_DMA Send Address Registers (DMA_UR4T_TXAx)

DMA_UR4T_TXA: Set the source address of automatic data transmission. Data is read from this address when

performing a UR4T_DMA operation.

23.8.7 UR4R_DMA Configuration Register (DMA_UR4R_CFG)

UR4RIE: UR4R_DMA interrupt enable control bit

0: Disable UR4R_DMA interrupt

1: Enable UR4R_DMA interrupt

UR4RIP[1:0]: UR4R_DMA interrupt priority control bits

UR4RPTY[1:0]: UR4R_DMA Data bus access priority control bits

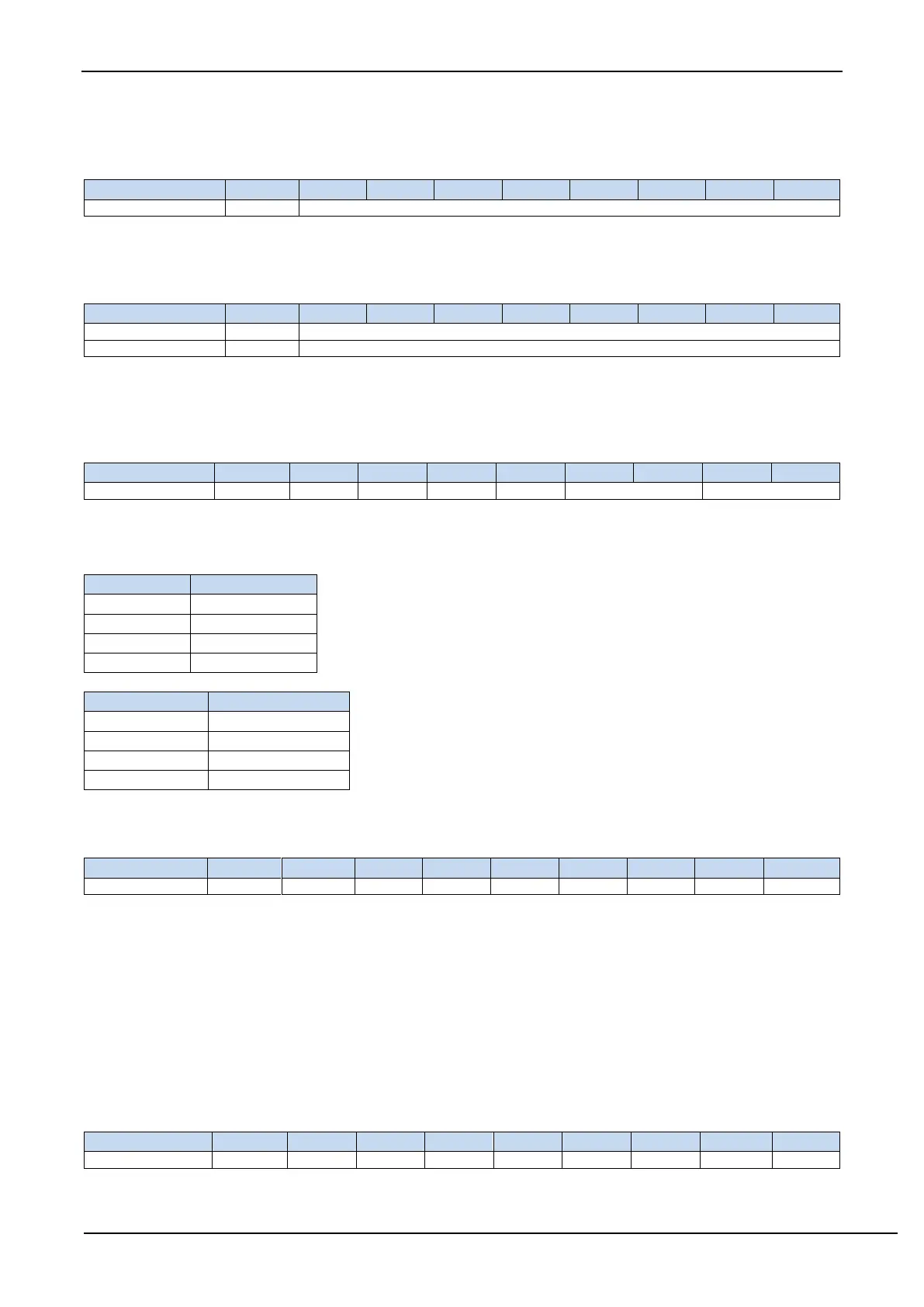

23.8.8 UR4R_DMA Control Register (DMA_UR4R_CR)

ENUR4R: UR4R_DMA function enable control bit

0: Disable UR4R_DMA function

1: Enable UR4R_DMA function

TRIG: UR4R_DMA UART1 receive trigger control bit

0: Write 0 is invalid

1: Write 1 to start UR4R_DMA receiving data automatically

CLRFIFO: Clear UR4R_DMA receive FIFO control bit

0: Write 0 is invalid

1: Before starting the UR4R_DMA operation, clear the built-in FIFO of the UR4R_DMA firstly

23.8.9 UR4R_DMA Status Register (DMA_UR4R_STA)

UR4RIF: UR4R_DMA interrupt request flag bit. When UR4R_DMA receives data, the hardware will automatically set

Loading...

Loading...