STC8A8K64D4 Series Manual

LCM_DMA Send High Address

LCM_DMA Receive High Address

LCM_DMA Receive Low Address

23.2 Data read and write between memory and memory (M2M_DMA)

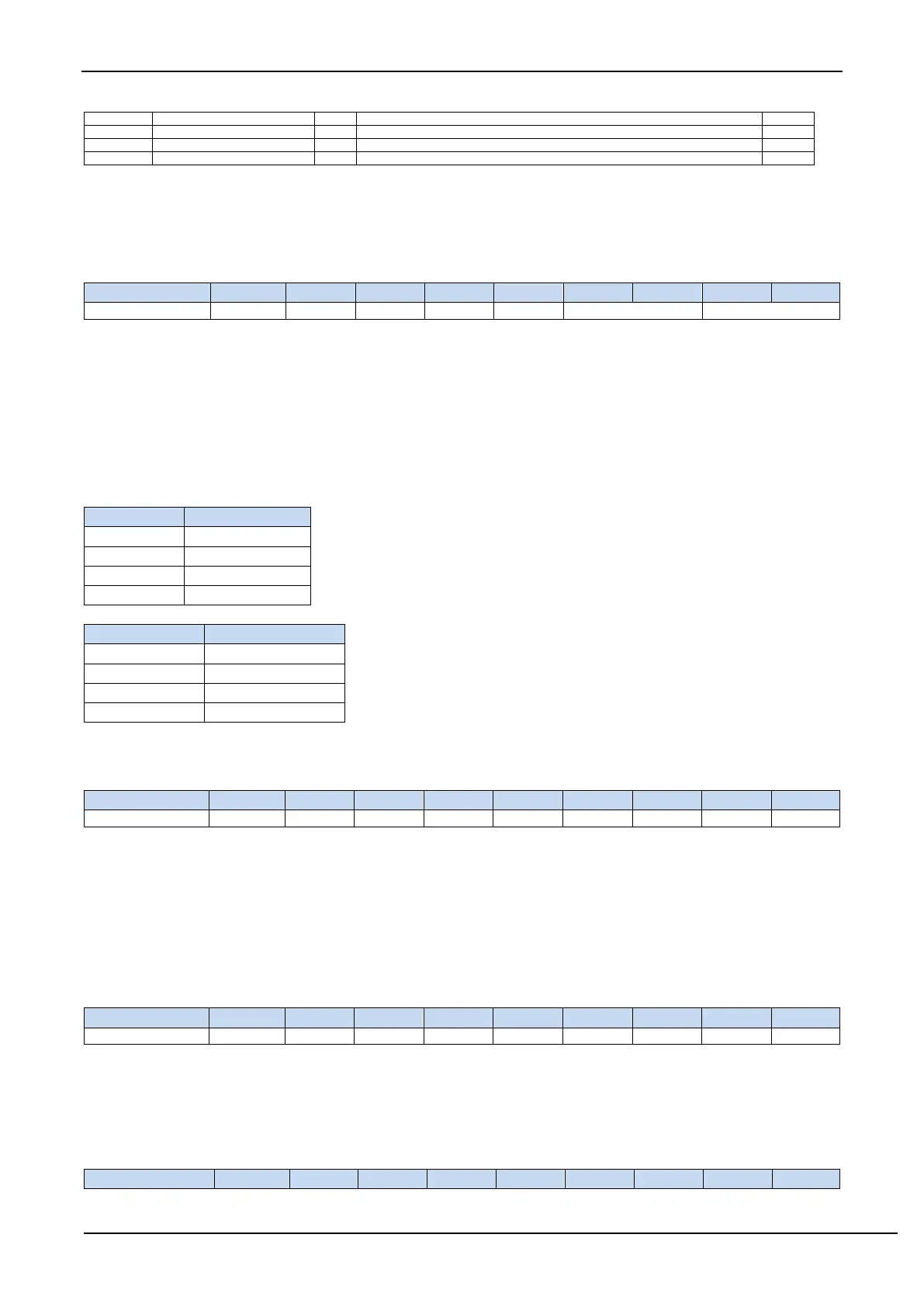

23.2.1 M2M_DMA Configuration Register (DMA_M2M_CFG)

M2MIE: M2M_DMA interrupt enable control bit

0: Disable M2M_DMA interrupt

1: Enable M2M_DMA interrupt

TXACO: M2M_DMA source address (read address) changes direction

0: The address is automatically incremented after the data read is completed

1: The address is automatically decremented after the data read is completed

RXACO: M2M_DMA target address (write address) changed direction

0: The address is automatically incremented after data writing is completed

1: The address is automatically decremented after data writing is completed

M2MIP[1:0]: M2M_DMA interrupt priority control bits

M2MPTY[1:0]: M2M_DMA Data bus access priority control bits

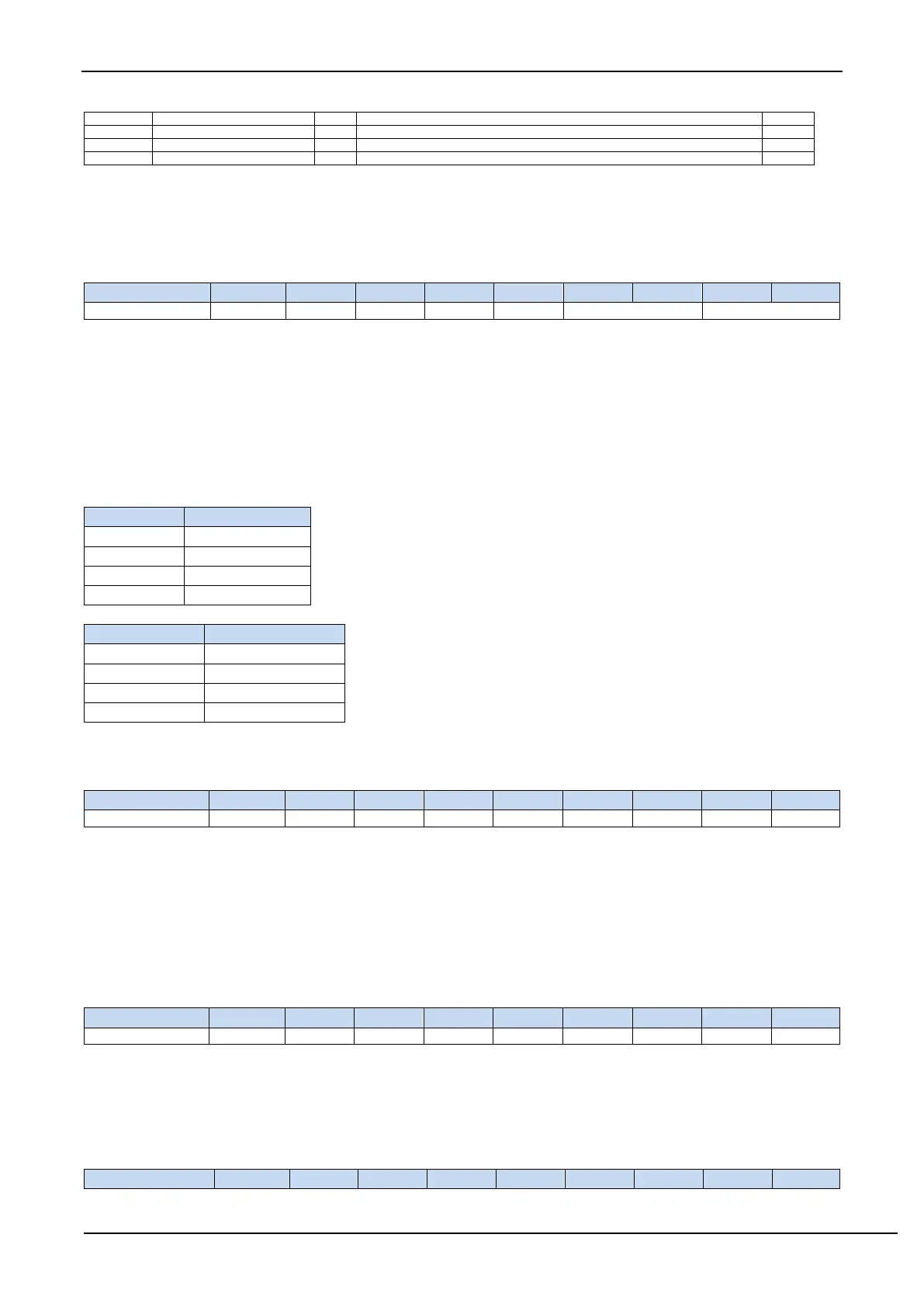

23.2.2 M2M_DMA Control Register (DMA_M2M_CR)

ENM2M: M2M_DMA function enable control bit

0: Disable M2M_DMA function

1: Enable M2M_DMA function

TRIG: M2M_DMA data read and write trigger control bit

0: Write 0 is invalid

1: Write 1 to start M2M_DMA operation.

23.2.3 M2M_DMA Status Register (DMA_M2M_STA)

M2MIF: M2M_DMA interrupt request flag bit. When the M2M_DMA operation is completed, the hardware

automatically sets M2MIF to 1, and if the M2M_DMA interrupt is enabled, the interrupt service routine is entered.

The flag bit needs to be cleared by software.

23.2.4 M2M_DMA transfer total byte register (DMA_M2M_AMT)

Loading...

Loading...