STC8A8K64D4 Series Manual

UR4RIF to 1. If the UR4R_DMA interrupt is enabled, it will enter the interrupt service routine. The flag bit needs

to be cleared by software

RXLOSS: UR4R_DMA receive data discard flag. During the UR4R_DMA operation, when the XRAM bus is too busy

to clear the receive FIFO of the UR4R_DMA and the data received by the UR4R_DMA is automatically discarded,

the hardware will automatically set RXLOSS to 1. The flag bit needs to be cleared by software

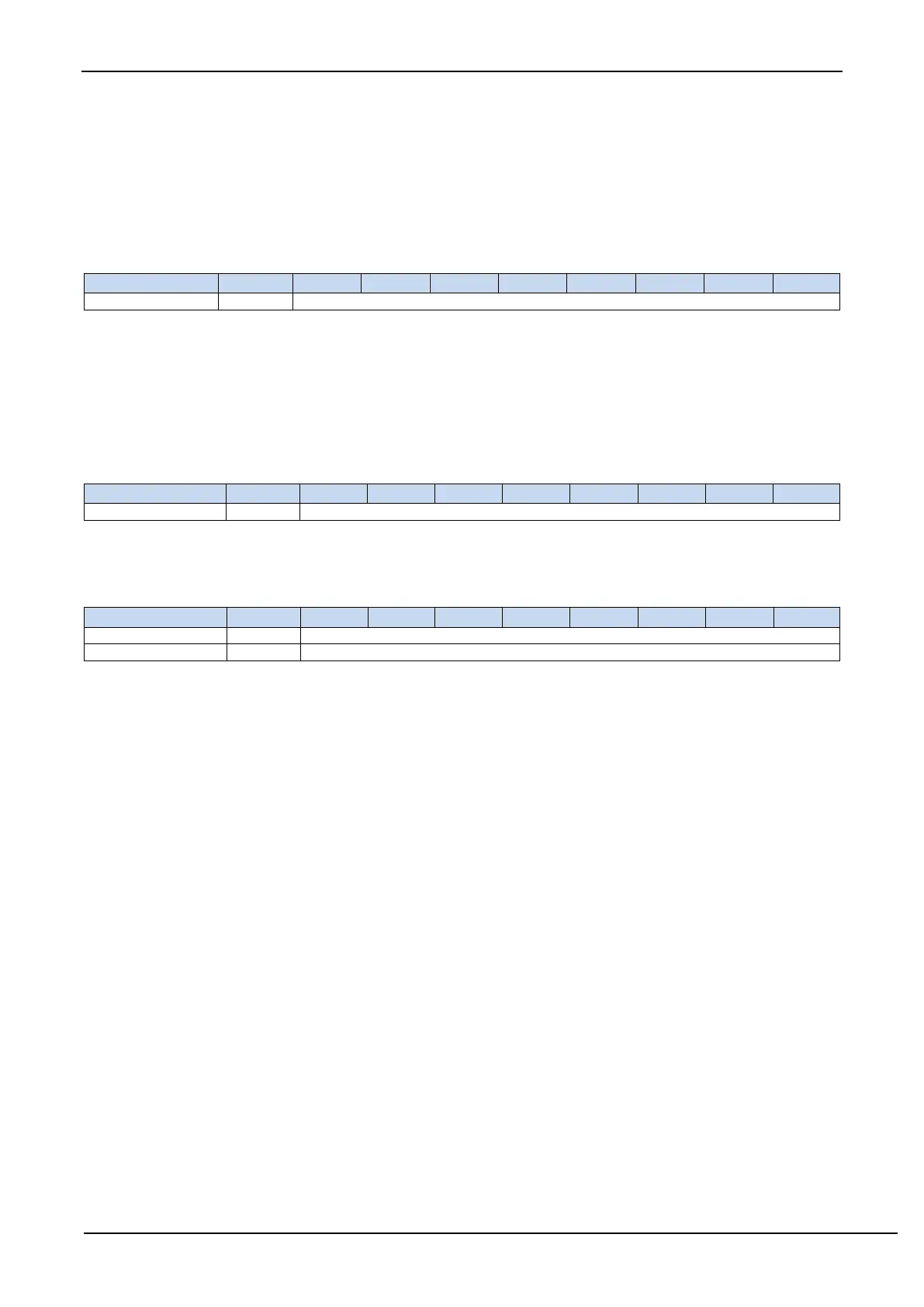

23.8.10 UR4R_DMA transfer total byte register (DMA_UR4R_AMT)

DMA_UR4R_AMT: Set the number of data bytes that need to automatically receive.

Note: The actual number of bytes is (DMA_UR4R_AMT+1), that is, when DMA_UR4R_AMT is set to 0, 1

byte is transferred, and when DMA_UR4R_AMT is set to 255, 256 bytes are transferred.

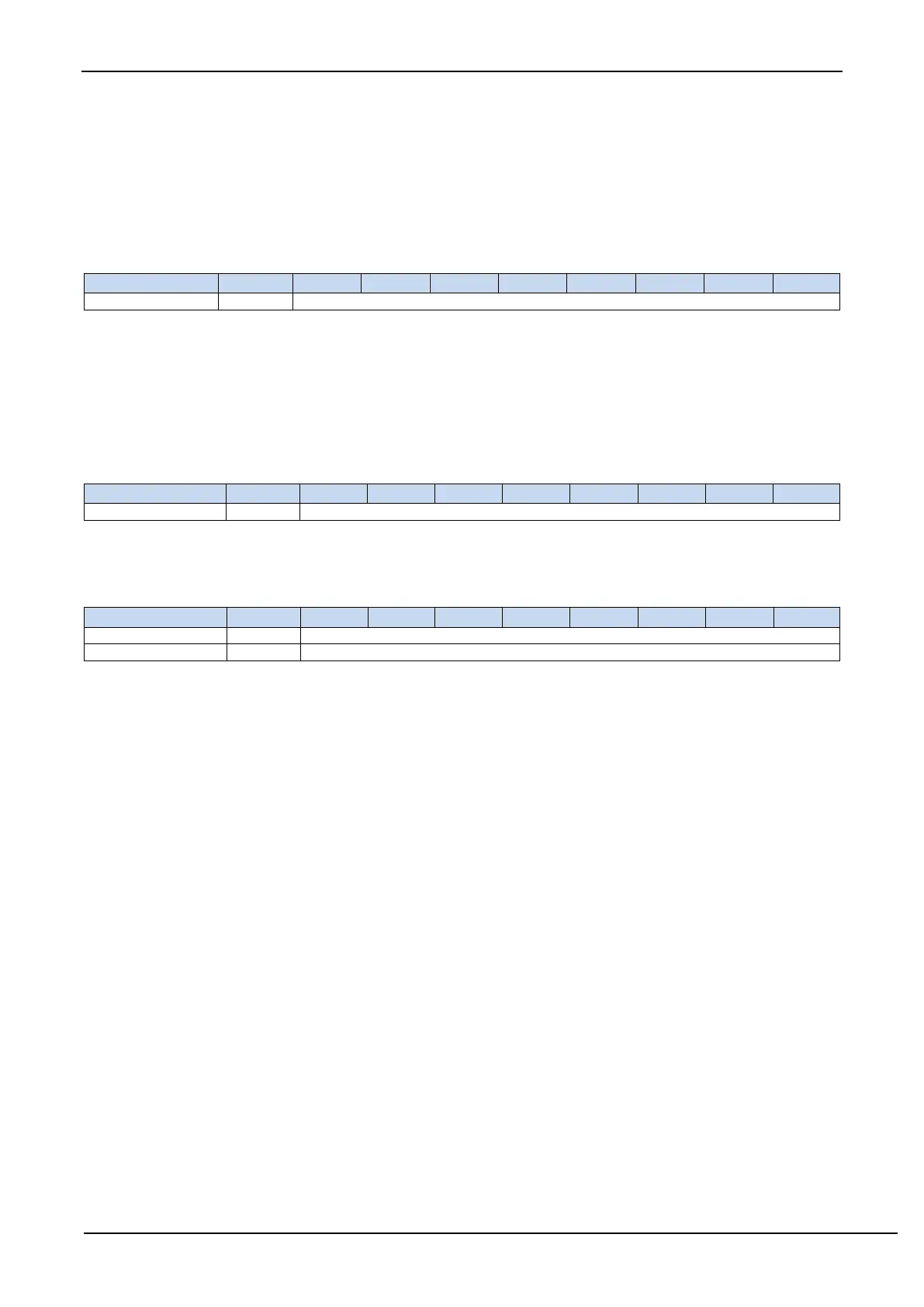

23.8.11 UR4R_DMA transfer complete byte register

(DMA_UR4R_DONE)

DMA_UR4R_DONE: The number of bytes that have been received currently.

23.8.12 UR4R_DMA Receive Address Registers (DMA_UR4T_RXAx)

DMA_UR4R_RXA: Set the target address for automatically receiving data. Data will be written from this address when

performing a UR4R_DMA operation.

Loading...

Loading...