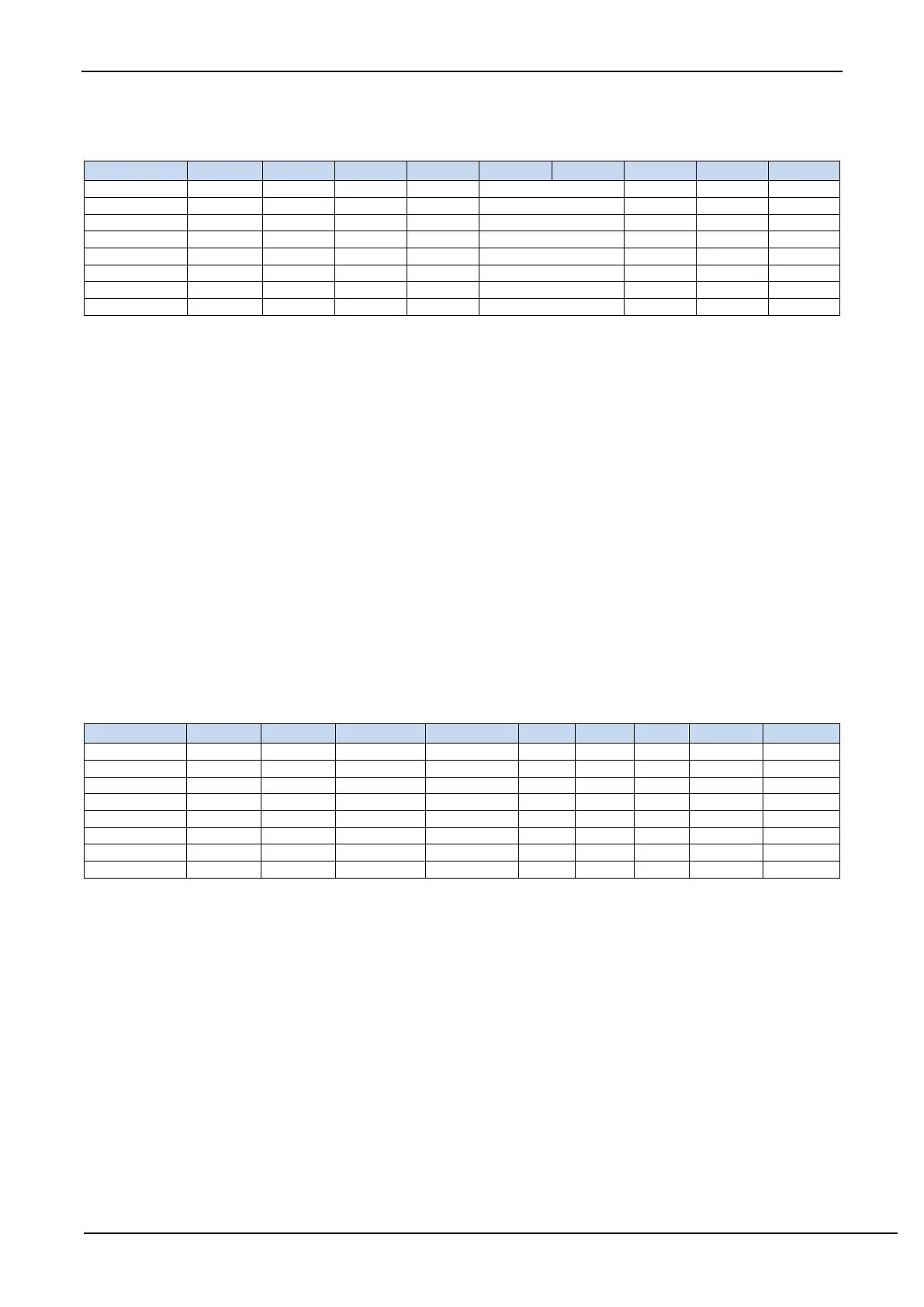

ENO: PWMi output enable bit. (i= 0~7)

0: the corresponding port of PWM channel i is GPIO.

1: the corresponding port of PWM channel i is PWM output port, which is controlled by the PWM waveform

generator.

INI: the initial level of PWMi output. (i= 0~7)

0: the initial level of PWM channel i is low.

1: the initial level of PWM channel i is high.

Ci_S[1:0] : Switch PWMi output pin (i=0~7)

For details, please refer to the chapter "Function Foot Switching".

ENI: interrupt enable bit of PWM channel i. (i= 0~7)

0: disable PWM channel i interrupt.

1: enable PWM channel i interrupt.

ENT2I: interrupt enable bit of the second flip point of PWM channel i. (i= 0~7)

0: disable the interrupt of the second flip point of PWM channel i.

1: enable the interrupt of the second flip point of PWM channel i.

ENT1I: interrupt enable bit of the first flip point of PWM channel i. (i= 0~7)

0: disable the interrupt of the first flip point of PWM channel i.

1: enable the interrupt of the first flip point of PWM channel i.

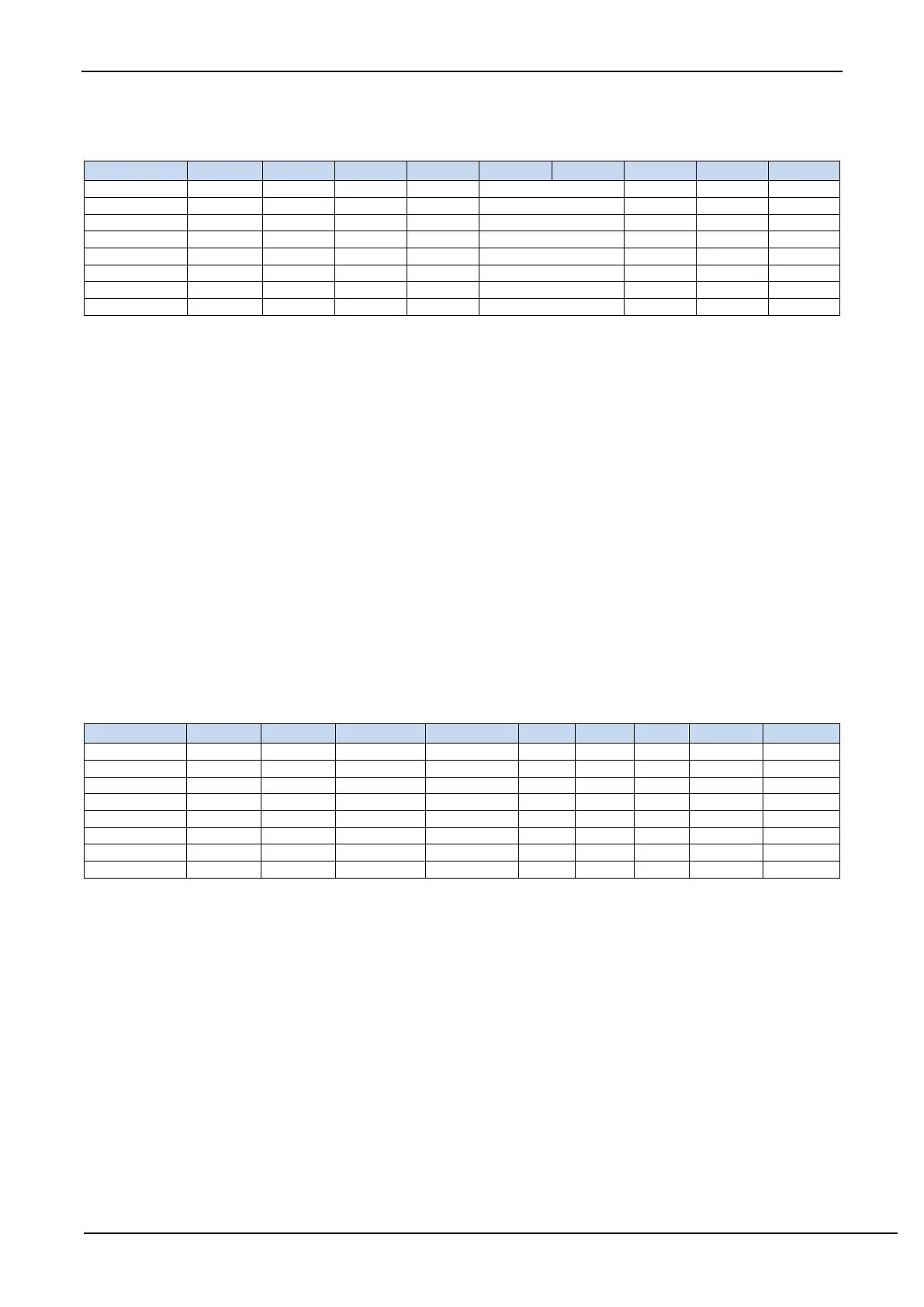

19.2.10 PWM Channel Level Holding Control Registers (PWMnHLD)

HLDH: PWM channel i outputs high compulsively control bit. (i= 0~7)

0: PWM channel i output normally.

1: PWM channel i outputs high compulsively.

HLDL: PWM channel i outputs low compulsively control bit. (i= 0~7)

0: PWM channel i output normally.

1: PWM channel i outputs low compulsively.

Loading...

Loading...