STC8A8K64D4 Series Manual

21.3 I

2

C Master Mode

21.3.1 I2C Configuration Register (I2CCFG)

ENI2C: I

2

C function enable bit

0: disable I

2

C function

1: enable I

2

Cfunction

MSSL: I

2

C mode selection bit

0: Salve mode

1: Master mode

MSSPEED[5:0]: I

2

C bus speed control bits (clocks to wait), I2C bus speed=F

OSC

/ 2 / (MSSPEED * 2 + 4)

The waiting parameter set by the MSSPEED is valid only when the I

2

C module is operating in the master mode.

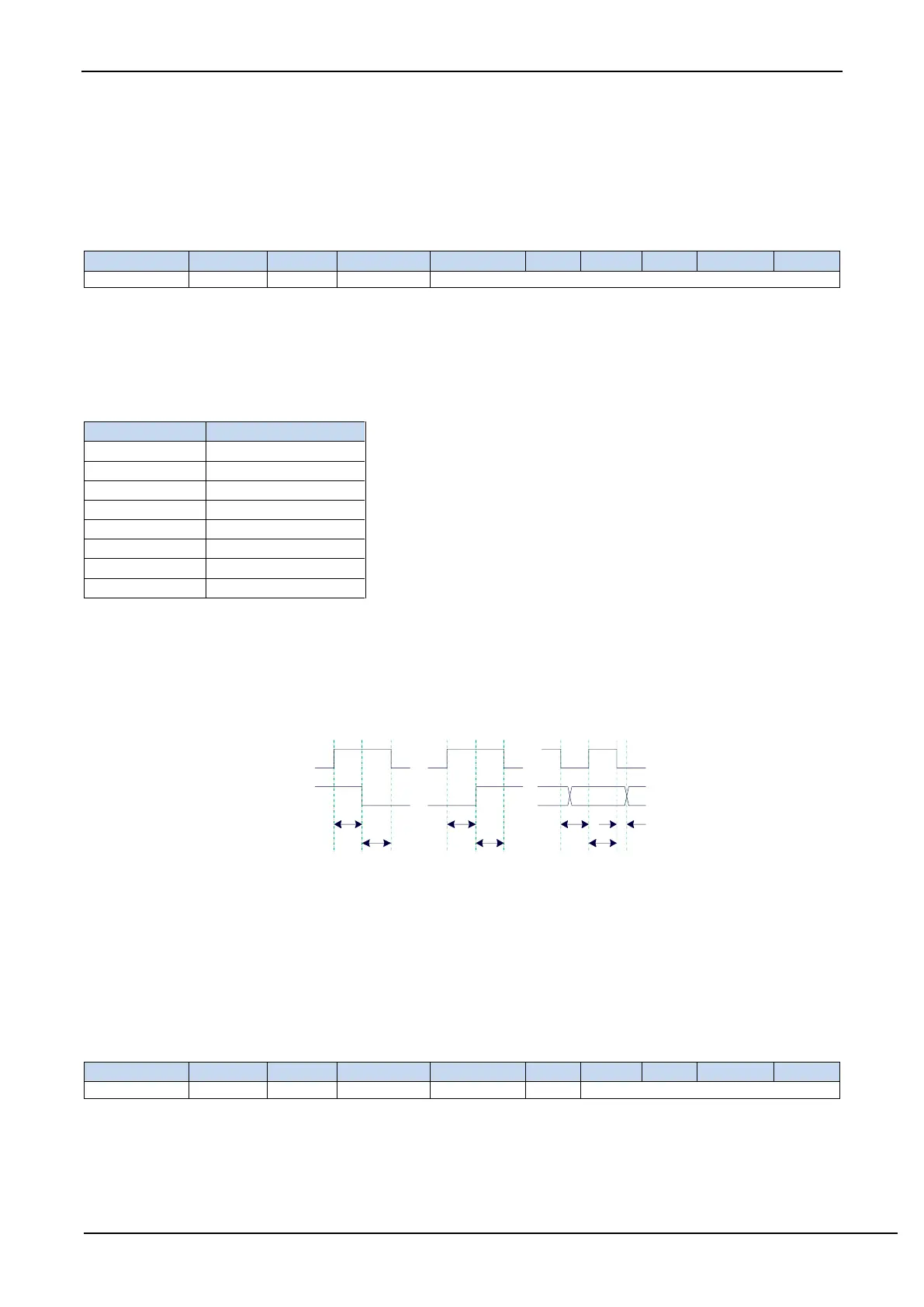

The waiting parameter is mainly used for the following signals in master mode:

T

SSTA

: Setup Time of START

T

HSTA

: Hold Time of START

T

SSTO

: Setup Time of STOP

T

HSTO

: Hold Time of STOP

T

HCKL:

Hold Time of SCL Low

SCL

SDA

T

SSTA

T

HSTA

START

T

SSTO

T

HSTO

STOP

T

HCKL

T

HCKH

DATA

Fixed to 1 clock

Example 1: When MSSPEED=10, T

SSTA

=T

HSTA

=T

SSTO

=T

HSTO

=T

HCKL

=24/FOSC

Example 2: When 400K I2C bus speed is required at 24MHz operating frequency,

MSSPEED=(24M / 400K / 2 - 4) / 2=13

21.3.2 I

2

C Master Control Register (I2CMSCR)

EMSI: Master mode interrupt enable control bit

0: disable master mode interrupt

1: enable master mode interrupt

MSCMD[3:0]: master command bits

0000: Standby, no action

Loading...

Loading...