STC8A8K64D4 Series Manual

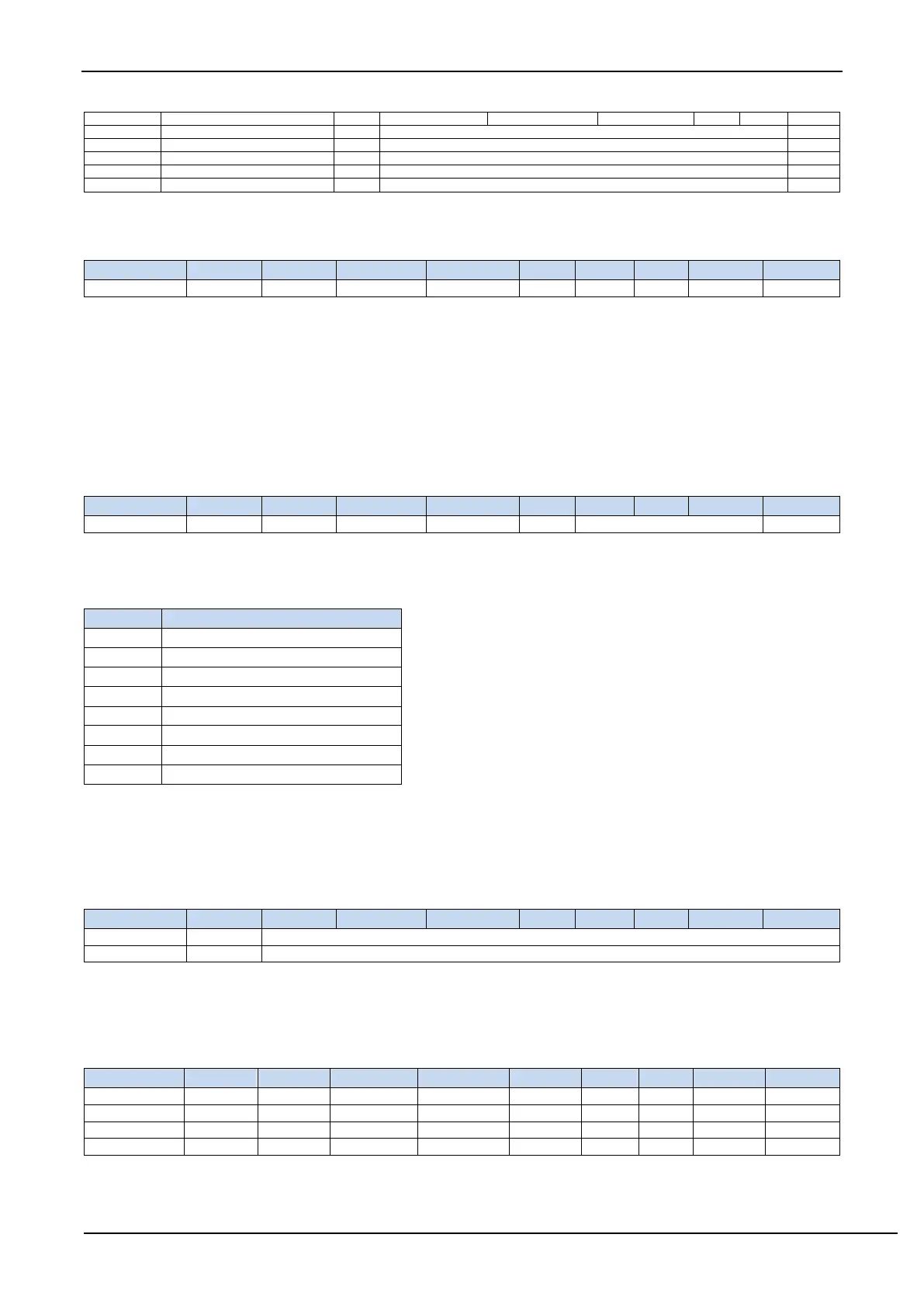

PCA 0 Capture Register High Byte

PCA 1 Capture Register High Byte

PCA 2 Capture Register High Byte

PCA 3 Capture Register High Byte

18.2.1 PCA control register (CCON)

CF: PCA Counter overflow flag. It is set by hardware when the 16-bit counter of PCA overflows, and requests interrupt

to CPU. It must be cleared by software.

CR: PCA counter enable bit.

0: Stop PCA counting.

1: Start PCA counting.

CCFn(n=0,1,2,3): PCA interrupt flag. When a match or a capture occurs on the PCA module, the corresponding flag

bit is set by the hardware automatically and requests an interrupt to CPU. These flags should be cleared by software.

18.2.2 PCA mode register (CMOD)

CIDL: PCA Counter control bit in Idle mode.

0: the PCA counter will continue counting in idle mode.

1: the PCA counter will stop counting in idle mode.

CPS[2:0]: PCA Counter pulse source select bits.

Input clock source of PCA

Overflow pulse of timer 0

External clock input from ECI pin

ECF: PCA counter overflow interrupt enable bit

0: disable PCA counter overflow interrupt

1: enable PCA counter overflow interrupt

18.2.3 PCA counter registers (CL, CH)

The 16-bit counter is the combination of CL and CH, where CL is the low 8-bit counter and CH is the high 8-bit counter.

The 16-bit counter of PCA increments automatically every one PCA clock.

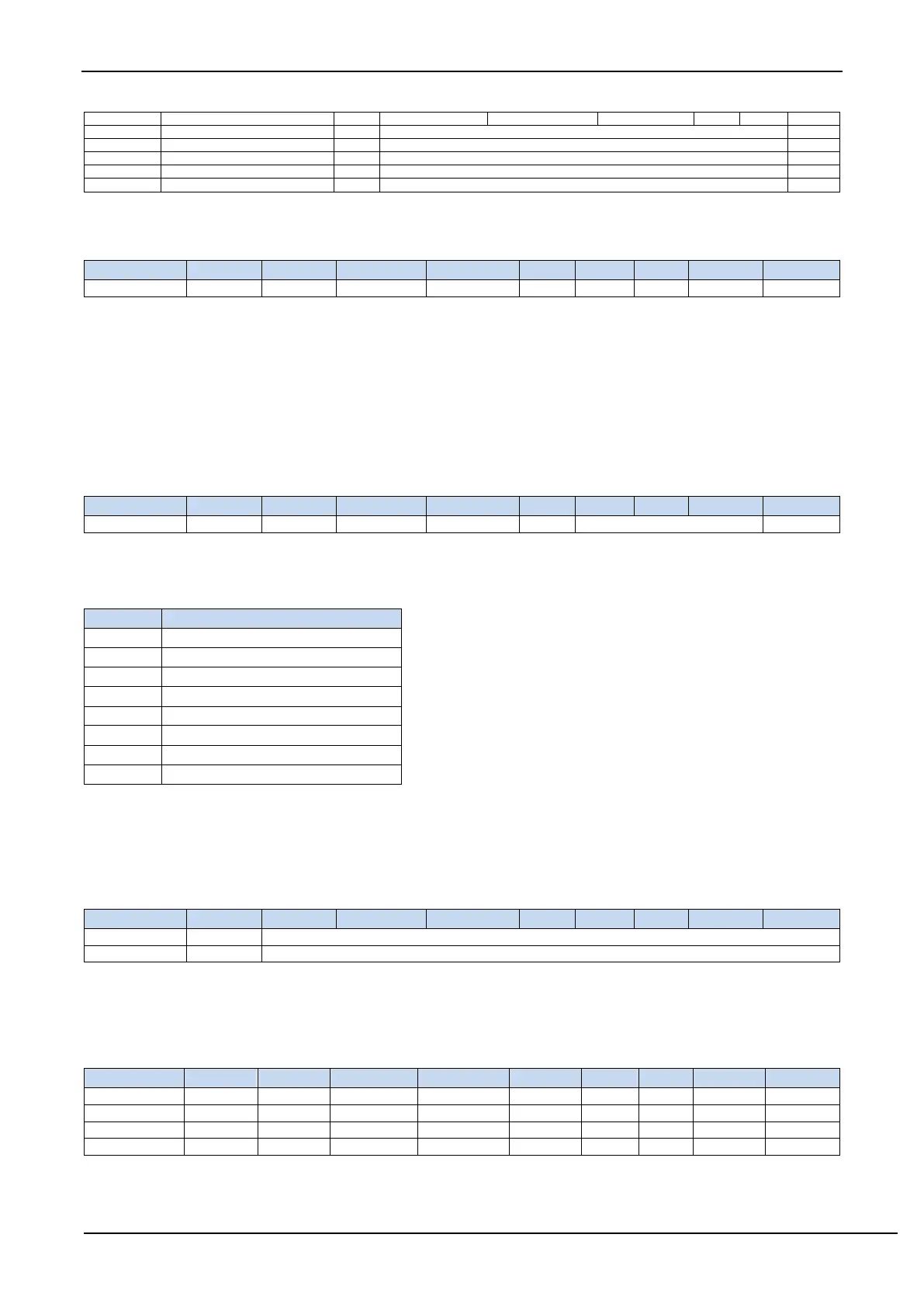

18.2.4 PCA mode control registers (CCAPMn)

ECOMn: PCAn Comparator enable bit

CCAPPn: PCAn Capture on rising edge enable bit

Loading...

Loading...