STC8A8K64D4 Series Manual

-

CLR_WDT: WDT clear bit.

0: No operation

1: WDT is cleared. This bit will be cleared by hardware automatically.

IDL_WDT: WDT control bit in IDLE mode.

0: WDT is disabled in IDLE mode.

1: WDT is enabled in IDLE mode, and the WDT will continue counting.

WDT_PS[2:0]: Watchdog timer clock division factor

The WDT overflow time is determined by the following equation:

WDT overflow time =

12 × 32768 × 2

(WDT_PS+1)

SYSclk

(s)

6.3.2 Software reset (IAP_CONTR)

IAP_CONTR (IAP Control Register)

SWBS: Software boot selection bit

0: The microcontroller executes the code from user program space (main flash memory) after the software reset. The data

in the user data space remains unchanged.

1: The microcontroller executes the code from ISP space after the software reset. The data in the user data space is

initialized.

SWRST: Software reset trigger bit.

0: No operation

1: Trigger software reset.

Writing 60H to the IAP control register can achieve the effect of cold start of the microcontroller

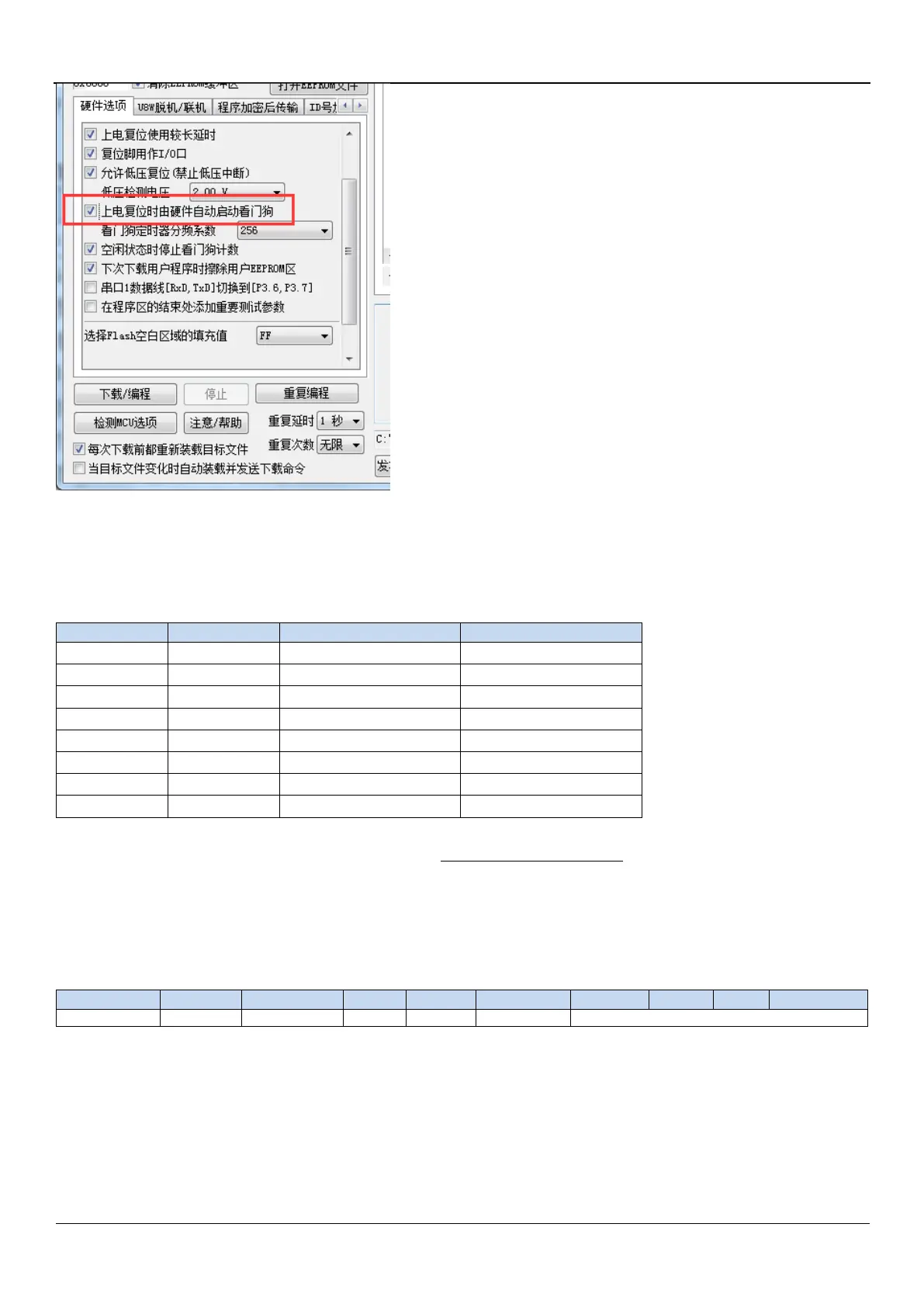

Loading...

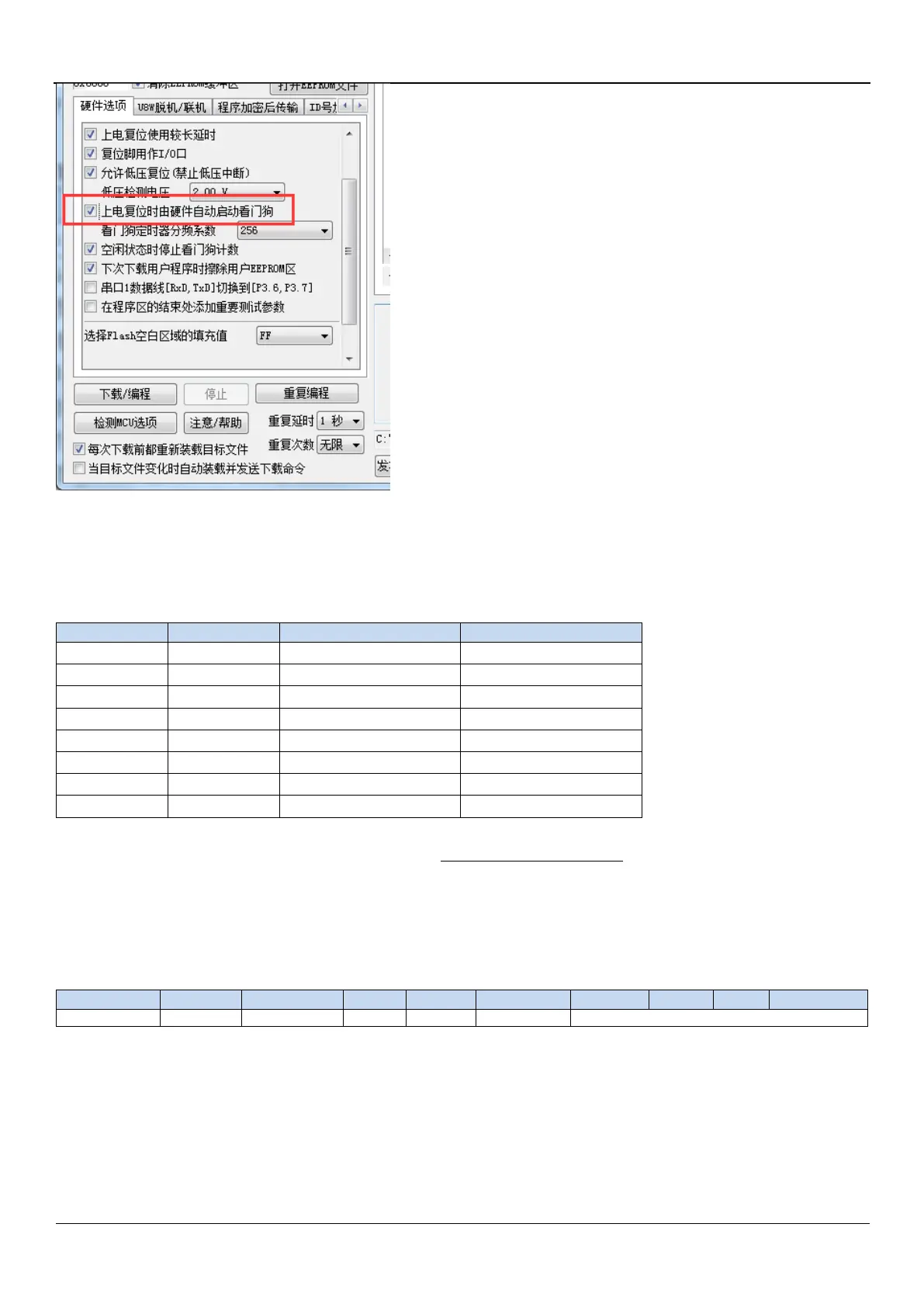

Loading...