STC8A8K64D4 Series Manual

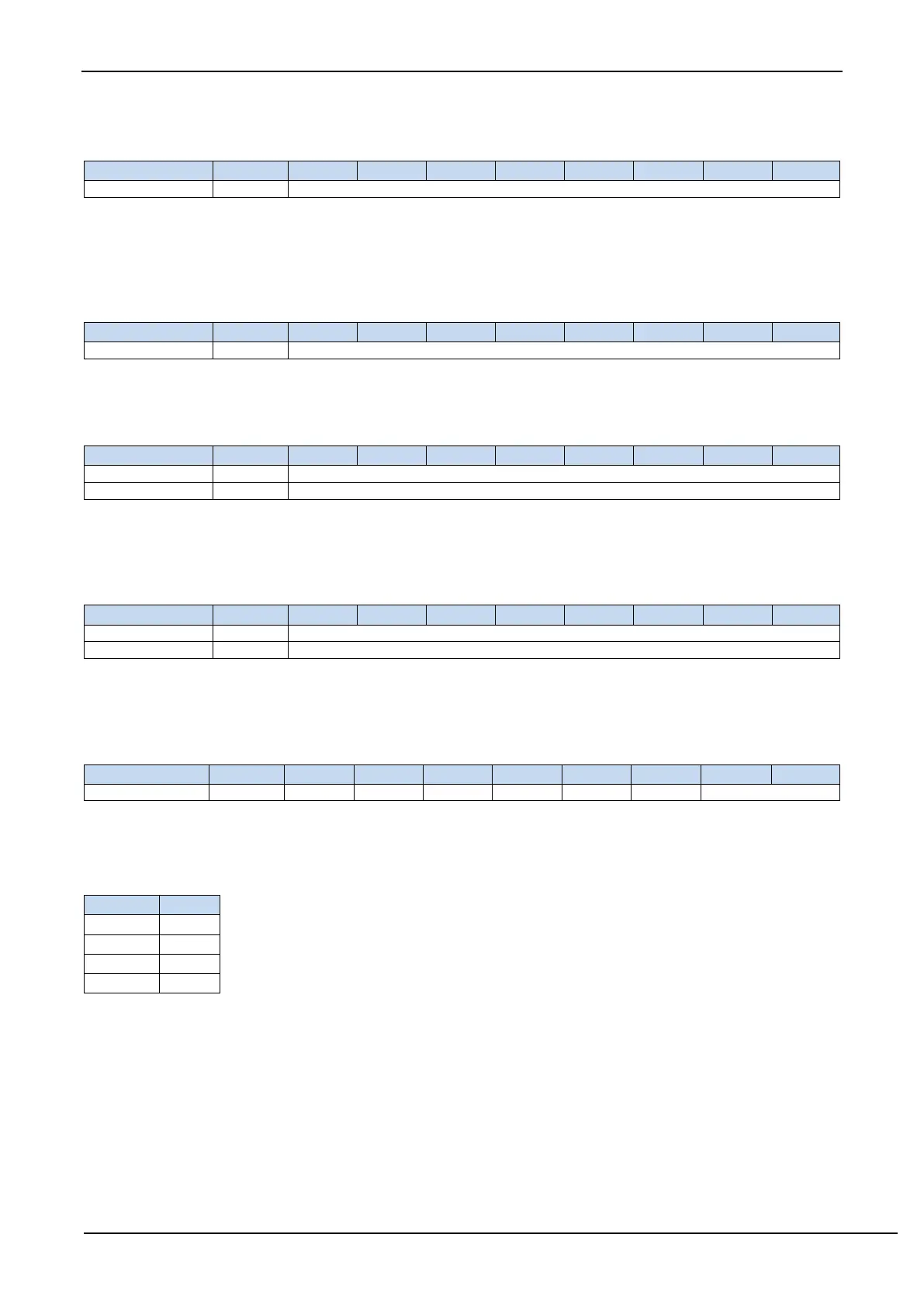

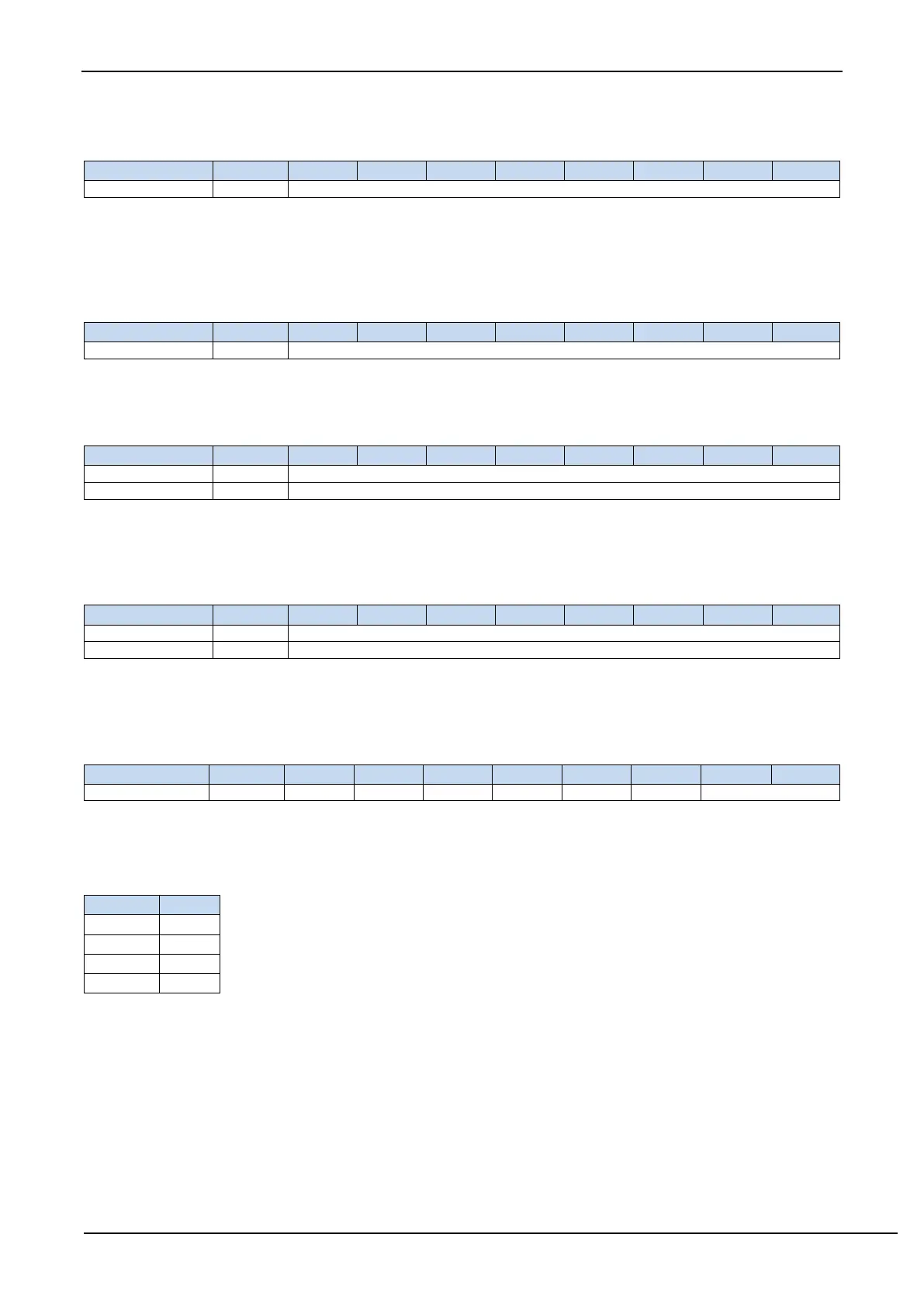

23.4.4 SPI_DMA transfer total byte register (DMA_SPI_AMT)

DMA_SPI_AMT: Set the number of bytes that need to read and write data.

Note: The actual number of bytes read and written is (DMA_SPI_AMT+1), that is, when DMA_SPI_AMT

is set to 0, 1 byte is transferred, and when DMA_SPI_AMT is set to 255, 256 bytes are transferred.

23.4.5 SPI_DMA transfer complete byte register (DMA_SPI_DONE)

DMA_SPI_DONE: The number of bytes that have been read and written currently.

23.4.6 SPI_DMA Send Address Registers (DMA_SPI_TXAx)

DMA_SPI_TXA: Set the source address when reading and writing data. Data will be read from this address when the

SPI_DMA operation is performed.

23.4.7 SPI_DMA Receive Address Registers (DMA_SPI_RXAx)

DMA_SPI_RXA: Set the target address when reading and writing data. Data will be written from this address when

the SPI_DMA operation is performed.

23.4.8 SPI_DMA Configuration Register 2 (DMA_SPI_CFG2)

WRPSS: Enable SS pin control bit during SPI_DMA process

0: During the SPI_DMA transfer process, the SS pin is not automatically controlled

1: During the SPI_DMA transfer process, the SS pin is automatically pulled down, and the original state is

automatically restored after the transfer is completed.

SSS[1:0]: During the SPI_DMA process, control the SS selection bit automatically

Loading...

Loading...